**ФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ**

**ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ**

**УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ**

**«САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ**

**ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М.А. БОНЧ-БРУЕВИЧА»**

**(СПбГУТ)**

**АРХАНГЕЛЬСКИЙ КОЛЛЕДЖ ТЕЛЕКОММУНИКАЦИЙ (ФИЛИАЛ) СПбГУТ**

**(АКТ (ф) СПбГУТ)**

УТВЕРЖДАЮ

Зам. директора по учебной работе

Н.В. Калинина

2018 г.

**Составил**

**Е.Г. Флейшман**

**ОП.04 ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА**

Программа, теоретические основы, методические указания по

изучению дисциплины, контрольное задание для

студентов заочной формы обучения

по специальности

11.02.09 – Многоканальные телекоммуникационные системы

Архангельск 2018

Е.Г. Флейшман. ОП.04 Вычислительная техника. Программа, теоретические основы, методические указания по изучению дисциплины, контрольное задание. - Архангельск. АКТ (ф) СПбГУТ, 2018.

Рассмотрено и одобрено цикловой комиссией Информационных технологий и математических дисциплин АКТ (ф) СПбГУТ.

Пособие содержит учебную карту дисциплины, задания для домашней контрольной работы, теоретические основы и методические указания по выполнению заданий, список использованных источников.

## СОДЕРЖАНИЕ

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| ПОЯСНИТЕЛЬНАЯ ЗАПИСКА                                                                        | 4   |

| 1. Учебная карта дисциплины ОП.04 Вычислительная техника                                     | 6   |

| 2. Введение.                                                                                 |     |

| Раздел 1. Математические и логические основы вычислительной<br>техники                       | 9   |

| 3. Раздел 2. Логические основы ЭВМ                                                           | 15  |

| 4. Раздел 3. Типовые узлы ЭВМ                                                                | 24  |

| 5. Раздел 4. Устройства ЭВМ                                                                  | 31  |

| 6. Раздел 5. Микропроцессоры (МП) и микропроцессорные<br>системы (МПС)                       | 31  |

| 7. Контрольная работа                                                                        | 33  |

| Приложение А. Общие правила построения УГО                                                   | 64  |

| Приложение Б. Третий элемент маркировки ИМС                                                  | 67  |

| Приложение В. Условное графическое обозначение микросхем<br>логических элементов и устройств | 68  |

| Приложение Г. Варианты алгоритмов для задания № 5<br>контрольной работы                      | 83  |

| Приложение Д. Принцип построения и функционирования схем<br>цифровых устройств               | 93  |

| 8. Экзаменационные вопросы по дисциплине                                                     |     |

| ОП.04 Вычислительная техника                                                                 | 101 |

| Список использованных источников                                                             | 103 |

## ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

Дисциплина ОП.04 Вычислительная техника является частью программы подготовки специалистов среднего звена в соответствии с ФГОС по специальности СПО 11.02.09 Многоканальные телекоммуникационные системы и входит в общепрофессиональный цикл.

Цель изучения дисциплины состоит в формировании базовой подготовки студентов в области цифровых устройств и микропроцессорных систем для изучения профилирующих дисциплин, развития навыков практического использования цифровой техники в современных системах связи. Цифровые методы обработки информации и цифровые устройства широко применяются в системах передачи и распределения информации, в телевизионной и радиовещательной аппаратуре.

Дисциплина ОП.04 Вычислительная техника является базой для дисциплин, связанных с вопросами аппаратной реализации устройств систем связи.

**В результате освоения дисциплины обучающийся должен:**

**уметь:**

- использовать типовые средства вычислительной техники и программного обеспечения в профессиональной деятельности;

- осуществлять перевод чисел из одной системы счисления в другую, применять законы алгебры логики;

- строить и использовать таблицы истинности логических функций, элементов и устройств;

**знать:**

- виды информации и способы ее предоставления в ЭВМ;

- логические основы ЭВМ, основы микропроцессорных систем;

- типовые узлы и устройства ЭВМ, взаимодействие аппаратного и программного обеспечения ЭВМ.

**Перечень формируемых компетенций:**

**Общие компетенции (ОК):**

ОК 1. Понимать сущность и социальную значимость своей будущей профессии, проявлять к ней устойчивый интерес.

ОК 2. Организовывать собственную деятельность, выбирать типовые методы и способы выполнения профессиональных задач, оценивать их эффективность и качество.

ОК 3. Принимать решения в стандартных и нестандартных ситуациях и нести за них ответственность.

- ОК 4. Осуществлять поиск и использование информации, необходимой для эффективного выполнения профессиональных задач, профессионального и личностного развития.

- ОК 5. Использовать информационно-коммуникационные технологии в профессиональной деятельности.

- ОК 6. Работать в коллективе и команде, эффективно общаться с коллегами, руководством, потребителями.

- ОК 7. Брать на себя ответственность за работу членов команды (подчиненных), результат выполнения заданий.

- ОК 8. Самостоятельно определять задачи профессионального и личностного развития, заниматься самообразованием, осознанно планировать повышение квалификации.

- ОК 9. Ориентироваться в условиях частой смены технологий в профессиональной деятельности.

#### **Профессиональные компетенции (ПК):**

- ПК 1.1. Выполнять монтаж и техническое обслуживание кабелей связи и оконечных кабельных устройств.

- ПК 1.2. Выполнять монтаж, первичную инсталляцию, мониторинг и диагностику цифровых и волоконно-оптических систем передачи.

- ПК 1.4. Проводить измерения параметров цифровых каналов, трактов, анализировать результаты измерений.

В процессе изучения дисциплины большая часть часов отводится на самостоятельную внеаудиторную работу, которая является основной частью усвоения дисциплины и выполняется в межсессионный период. Самостоятельная внеаудиторная работа включает изучение теоретического материала и ознакомление с решением типовых задач, выполнение одной домашней контрольной работы.

Для успешного выполнения контрольной работы студент должен самостоятельно изучить соответствующий теоретический материал и ознакомиться с решением типовых задач, приведенных в настоящем пособии. Контрольная работа составлена так, что если студент выполняет её самостоятельно, то подготовка его к экзамену займет небольшое время.

Работа должна быть оформлена аккуратно в отдельной ученической тетради в клетку с отчерченными полями, все страницы должны быть пронумерованы. Последовательность заполнения тетради: условие задачи №1

(полностью)- ее решение, условие задачи №2 (полностью)- ее решение и т.д. После решения последней задачи приводится список использованных источников, личная подпись и дата выполнения работы. Работа высыпается на рецензирование в соответствии с учебным графиком. После получения зачтенной работы студент должен внести исправления в соответствии с рецензией и показать их преподавателю во время экзаменационной сессии до экзамена. Если работа не зачтена, то в этой же тетради должны быть заново решены задачи, указанные преподавателем; затем тетрадь высыпается для повторного рецензирования.

При оценивании домашней контрольной работы студента учитывается следующее: качество выполнения практической части работы, качество оформления отчета по контрольной работе.

Работа оценивается следующим образом: «зачёт» - 80%-100% правильных ответов, «незачёт» - менее 80% правильных ответов. Стоимость каждого задания 1 балл. За правильное и логичное изложение ответа студент получает 1 балл. Если ответ правильный, но содержание и форма ответа имеют отдельные неточности, студент получает 0,5 балла. За неверный ответ или его отсутствие баллы не начисляются.

**Без представленной зачтенной контрольной работы студенты к сдаче экзамена не допускаются.**

# 1 Учебная карта дисциплины ОП.04 Вычислительная техника

| Наименование разделов и тем                                                                           | Максимальная нагрузка студента | Самостоятельно | Количество часов |                      |                      |

|-------------------------------------------------------------------------------------------------------|--------------------------------|----------------|------------------|----------------------|----------------------|

|                                                                                                       |                                |                | обзорные         | Аудиторных           |                      |

|                                                                                                       |                                |                |                  | Лабораторные занятия | Практические занятия |

| <b>Раздел 1. Информационные основы ЭВМ</b>                                                            | 22                             | 22             |                  |                      |                      |

| Тема 1.1 Введение                                                                                     | 3                              | 3              |                  |                      |                      |

| Тема 1.2 Кодирование информации                                                                       | 4                              | 4              |                  |                      |                      |

| Тема 1.3 Системы счисления                                                                            | 6                              | 6              |                  |                      |                      |

| Тема 1.4 Выполнение арифметических операций                                                           | 9                              | 9              |                  |                      |                      |

| <b>Раздел 2. Логические основы ЭВМ</b>                                                                | 29                             | 23             | 4                |                      | 2                    |

| Тема 2.1 Логические функции и схемы                                                                   | 12                             | 10             | 2                |                      |                      |

| Тема 2.2 Синтез логических устройств                                                                  | 11                             | 7              | 2                |                      |                      |

| <i>Практическое занятие</i><br>Синтез комбинационного логического устройства с применением карт Карно |                                |                |                  |                      | 2                    |

| Тема 2.3 Программы компьютерного моделирования                                                        | 6                              | 6              |                  |                      |                      |

| <b>Раздел 3. Типовые узлы ЭВМ</b>                                                                     | 64                             | 46             | 4                | 14                   |                      |

| Тема 3.1 Шифраторы и дешифраторы                                                                      | 9                              | 4              | 1                |                      |                      |

| <i>Лабораторная работа</i><br>Исследование шифраторов                                                 |                                |                |                  |                      | 2                    |

| <i>Лабораторная работа</i><br>Исследование дешифраторов                                               |                                |                |                  |                      | 2                    |

| Тема 3.2 Мультиплексоры и демультиплексоры                                                            | 10                             | 5              | 1                |                      |                      |

| <i>Лабораторная работа</i><br>Исследование мультиплексоров                                            |                                |                |                  |                      | 2                    |

| <i>Лабораторная работа</i><br>Моделирование электронного коммутатора                                  |                                |                |                  |                      | 2                    |

| Наименование разделов и тем                                                   | Максимальная нагрузка студента | Самостоятельно | Количество часов |            |                      |

|-------------------------------------------------------------------------------|--------------------------------|----------------|------------------|------------|----------------------|

|                                                                               |                                |                | обзорные         | Аудиторных | Лабораторные занятия |

| <b>Тема 3.3 Триггеры в интегральном исполнении</b>                            | 8                              | 6              |                  |            |                      |

| <i>Лабораторная работа</i><br>Исследование триггеров                          |                                |                |                  | 2          |                      |

| <b>Тема 3.4 Регистры</b>                                                      | 7                              | 4              | 1                |            |                      |

| <i>Лабораторная работа</i><br>Исследование регистров                          |                                |                |                  | 2          |                      |

| <b>Тема 3.5 Счетчики</b>                                                      | 9                              | 6              | 1                |            |                      |

| <i>Лабораторная работа</i><br>Исследование интегральных счетчиков             |                                |                |                  | 2          |                      |

| <b>Тема 3.6 Сумматоры</b>                                                     | 6                              | 6              |                  |            |                      |

| <b>Тема 3.7 Кодопреобразователи, ПЛМ, ПЛИС</b>                                | 6                              | 6              |                  |            |                      |

| <b>Тема 3.8 Распределители, синхрогенераторы, цифровые компараторы</b>        | 6                              | 6              |                  |            |                      |

| <b>Тема 3.9 Аналогово-цифровые и цифроаналоговые преобразователь</b>          | 3                              | 3              |                  |            |                      |

| <b>Раздел 4. Устройства ЭВМ</b>                                               | 19                             | 19             |                  |            |                      |

| <b>Тема 4.1 Запоминающие устройства ЭВМ</b>                                   | 8                              | 8              |                  |            |                      |

| <b>Тема 4.2 Процессоры ЭВМ</b>                                                | 8                              | 8              |                  |            |                      |

| <b>Тема 4.3 Интерфейсы в ВТ</b>                                               | 3                              | 3              |                  |            |                      |

| <b>Раздел 5. Микропроцессоры МП и микропроцессорные системы МПС</b>           | 10                             | 10             |                  |            |                      |

| <b>Тема 5.1 Архитектура МП</b>                                                | 3                              | 3              |                  |            |                      |

| <b>Тема 5.2 Архитектура МПС</b>                                               | 4                              | 4              |                  |            |                      |

| <b>Тема 5.3 Применение средств вычислительной техники СВТ в технике связи</b> | 3                              | 3              |                  |            |                      |

| <b>Всего часов:</b>                                                           | <b>144</b>                     | <b>120</b>     | <b>8</b>         | <b>14</b>  | <b>2</b>             |

## Введение

Основные сведения в ВТ. Понятие вычислительного устройства. История развития ВТ. Классификация вычислительных устройств. Задачи курса.

# РАЗДЕЛ 1. МАТЕМАТИЧЕСКИЕ И ЛОГИЧЕСКИЕ ОСНОВЫ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

## Тема 1.2. Кодирование информации

Кодирование информации. Коды. Применение в ЭВМ. Двоичные, позиционные, комбинационные, самокорректирующиеся, параллельные, последовательные. Признаки сигнала: амплитудный, фазовый, полярный, частотный, временной, импульсный. Формы представления чисел: с фиксированной и плавающей точкой.

## Тема 1.3. Системы счисления

Системы счисления. Позиционные системы счисления: 10, 2, 8, 16, 2-10. Перевод из одной системы счисления в другую. Формы представления чисел в ЭВМ.

Цифровые технологии используют разнообразные системы счисления, наиболее распространены десятичная, двоичная, восьмеричная и шестнадцатеричная. Десятичная система счисления, естественно, наиболее значима для нас. Изучение некоторых характеристик десятичной системы поможет лучше понять другие системы счисления, так как все эти системы являются позиционными.

### Десятичная система счисления

#### Основание системы счисления - 10

Десятичная система счисления состоит из десяти цифр - символов: 0,1,2,3,4,5,6,7,8,9. Используя их в качестве разрядов числа, можно выразить любую величину. Значение разряда зависит от его положения. Например: десятичное число 453 представляет 4 сотни, 5 десятков, 3 единицы. 4-старший значащий разряд (СЗР) - несет на себе вес всех трех разрядов. Число 3 - несет наименьший вес и называется младшим значащим разрядом (МЗР).

Любое число - это сумма произведений каждого разряда на его позиционную величину.  $4 \cdot 10^2 + 5 \cdot 10^1 + 3 \cdot 10^0$ .

Позиционные значения (веса)  $10^3$   $10^2$   $10^1$   $10^0$ ,  $10^{-1}$   $10^{-2}$   $10^{-3}$  и т. д.

целая часть числа    десят. запятая    дробн. часть числа

## Двоичная система счисления

## Основание системы счисления 2.

Существует только два символа: 0, 1.

В двоичной системе можно выразить любую величину, но требуется большое количество разрядов. Каждый разряд имеет свое собственное значение или вес, выраженный степенью 2. Позиции слева от двоичной точки (запятой) являются положительными степенями цифры 2, а места справа – отрицательными.

Позиционные значения (веса).  $2^3 2^2 2^1 2^0, 2^{-1} 2^{-2} 2^{-3}$  т.д.

целая часть числа    дв. запятая    дробная часть числа

| Степень 2                            | $2^{10}$ | $2^9$ | $2^8$ | $2^7$ | $2^6$ | $2^5$ | $2^4$ | $2^3$ | $2^2$ | $2^1$ | $2^0$ | $2^{-1}$ | $2^{-2}$ | $2^{-3}$ | $2^{-4}$ |

|--------------------------------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------|----------|----------|----------|

| Значение веса в 10 системе счисления | 1024     | 512   | 256   | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     | 0.5      | 0.25     | 0.125    | 0.0625   |

## Восьмеричная система счисления

Основные системы счисления 8

Состоит из восьми возможных цифр 0,1,2,3,4,5,6,7

Позиции разрядов восьмеричного числа имеют следующие веса:

и т.д.  $8^4 8^3 8^2 8^1$ ,  $8^{-1} 8^{-2} 8^{-3} 8^{-4}$  и т.д.

целая часть восьм. запят. дробная часть

| Степень 8                            | $8^5$ | $8^4$ | $8^3$ | $8^2$ | $8^1$ | $8^0$ | $8^{-1}$ | $8^{-2}$ | $8^{-3}$ |

|--------------------------------------|-------|-------|-------|-------|-------|-------|----------|----------|----------|

| Значение веса в 10 системе счисления | 32768 | 4096  | 512   | 64    | 8     | 1     | 0.125    | 0.015625 | 0.00195  |

## Шестнадцатеричная система счисления

Основные системы счисления 16

Состоит из 16 возможных символов: цифры от 0 до 9 и буквы A, B, C, D, E, F

Позиции разрядов шестнадцатеричного числа имеют следующие веса:

и т.д.  $16^3 16^2 16^1 16^0$ ,  $16^{-1} 16^{-2} 16^{-3} 16^{-4}$  и т.д.

целая часть      шестн. запят.      дробная часть

| Степень<br>16                                 | $16^4$ | $16^3$ | $16^2$ | $16^1$ | $16^0$ | $16^{-1}$ | $16^{-2}$ | $16^{-3}$ |

|-----------------------------------------------|--------|--------|--------|--------|--------|-----------|-----------|-----------|

| Значение<br>веса в 10<br>системе<br>счисления | 65536  | 4096   | 256    | 16     | 1      | 0.0625    | 0.00390   | 0.00024   |

## Двоично-десятичный код

Когда числа, буквы или слова представлены специальной группой символов, говорят, что они закодированы, а такую группу чисел и слов называют кодом. Например, код Морзе, в котором последовательность точек и тире представляют буквы алфавита. Если каждый разряд десятичного числа представить двоичном эквивалентом, то результат получим в виде кода, который называется двоично-десятичным кодом (Binary - Coded -Decimal - BCD) Так как десятичный разряд может быть равен 9 - требуется четыре бита, чтобы закодировать каждый разряд. Двоичный код 9 равен 1001, десятичное число 943 имеет двоично - десятичный код.

1001 0100 001

9      4      3

Таблица соотношений между десятичной, двоичной, восьмеричной, шестнадцатеричной системами счисления

| Десятич-<br>ная<br>система<br>счисле-<br>ния | Двоично-<br>десятичная<br>система | Двоич-<br>ная<br>система | Восьме-<br>ричная<br>система | Двоичное<br>представление<br>коэф. восьм.<br>системы | Шестнадца-<br>теричная<br>система | Двоичное<br>представление коэф.<br>шестн. системы |

|----------------------------------------------|-----------------------------------|--------------------------|------------------------------|------------------------------------------------------|-----------------------------------|---------------------------------------------------|

| 0                                            | 0000                              | 0                        | 0                            | 000                                                  | 0                                 | 0000                                              |

| 1                                            | 0001                              | 1                        | 1                            | 001                                                  | 1                                 | 0001                                              |

| 2                                            | 0010                              | 10                       | 2                            | 010                                                  | 2                                 | 0010                                              |

| 3                                            | 0011                              | 11                       | 3                            | 011                                                  | 3                                 | 0011                                              |

| 4                                            | 0100                              | 100                      | 4                            | 100                                                  | 4                                 | 0100                                              |

| 5                                            | 0101                              | 101                      | 5                            | 101                                                  | 5                                 | 0101                                              |

| 6                                            | 0110                              | 110                      | 6                            | 110                                                  | 6                                 | 0110                                              |

| 7                                            | 0111                              | 111                      | 7                            | 111                                                  | 7                                 | 0111                                              |

| 8                                            | 1000                              | 1000                     | 10                           | 001000                                               | 8                                 | 1000                                              |

| 9                                            | 1001                              | 1001                     | 11                           | 001001                                               | 9                                 | 1001                                              |

| 10                                           | 00010000                          | 1010                     | 12                           | 001010                                               | A                                 | 1010                                              |

| 11                                           | 00010001                          | 1011                     | 13                           | 001011                                               | B                                 | 1011                                              |

| 12                                           | 00010010                          | 1100                     | 14                           | 001100                                               | C                                 | 1100                                              |

| 13                                           | 00010011                          | 1101                     | 15                           | 001101                                               | D                                 | 1101                                              |

| 14                                           | 00010100                          | 1110                     | 16                           | 001110                                               | E                                 | 1110                                              |

| 15                                           | 00010101                          | 1111                     | 17                           | 001111                                               | F                                 | 1111                                              |

## Перевод чисел из одной системы счисления в другую

### Преобразование чисел из двоичной, восьмеричной, шестнадцатеричной в десятичную систему счисления

Двоичная восьмеричная, шестнадцатеричная системы счисления являются позиционными, т.е. каждый разряд несёт определенный вес, зависящий от его положения, относительно младшего значащего бита (мзб). Следовательно, любое из чисел может быть переведено в десятичный эквивалент с помощью умножения каждого разряда на его позиционный вес и суммирования этих произведений.

Перевести в десятичный эквивалент:

1. Двоичное число  $11011,01_2$

$$\begin{aligned} 11011,01_2 &= 1 \cdot 2^4 + 1 \cdot 2^3 + 0 \cdot 2^2 + 1 \cdot 2^1 + 1 \cdot 2^0 + 1 \cdot 2^{-1} + 1 \cdot 2^{-2} = \\ &= 1 \cdot 16 + 1 \cdot 8 + 0 \cdot 4 + 1 \cdot 2 + 1 \cdot 1 + 0 \cdot 1/2 + 1 \cdot 1/4 = 16 + 8 + 2 + 1 + \\ &0.25 = 27.25_{10} \end{aligned}$$

2. Восьмеричное число  $124.6_8$

$$\begin{aligned} 124.6_8 &= 1 \cdot 8^2 + 2 \cdot 8^1 + 4 \cdot 8^0 + 1 \cdot 8^{-1} = 1 \cdot 64 + 2 \cdot 8 + 4 \cdot 1 + 6/8 = \\ &= 64 + 16 + 4 + 0.75 = 84.75_{10} \end{aligned}$$

3.  $2AE,F_{16} = 2 \cdot 16^2 + A \cdot 16^1 + E \cdot 16^0 + F \cdot 16^{-1} = 2 \cdot 256 + 10 \cdot 16 + 14 \cdot 1 + 15/16 =$

$$= 512 + 160 + 14 + 15/16 = 512 + 160 + 14 + 0.937 = 685.937_{10}$$

4. Число в двоично-десятичном коде:

$$\underbrace{0101}_{5}, \underbrace{1000}_{8}, \underbrace{0111}_{7} = 58.7_{10}$$

5      8      7

### Преобразование из шестнадцатеричной, восьмеричной систем счисления - в двоичную. Из двоичной системы счисления - в восьмеричную и шестнадцатеричную

Перед выполнением этих преобразований необходимо помнить, что каждый восьмеричный разряд конвертируется в трехбитовый эквивалент двоичного, каждый шестнадцатеричный разряд конвертируется в четырехбитовый эквивалент.

$$375,21_8 = 011\ 111\ 101, 010\ 011_2 = 011111101,01000100_2 = FD,44_{16}$$

A    B    3    F

$$AB,3F_{16} = 1010\ 1011, 0011\ 1111_2 = 10101011,00111111_2 = 253,176_8$$

Преобразование двоичных чисел в восьмеричные или шестнадцатеричные повторяет рассмотренные преобразования, но в обратном порядке: разряды двоичного числа распределяются в группы по три бита влево и вправо от запятой - в случае перевода в восьмеричную систему; по четыре бита - в случае перевода в шестнадцатеричную, затем каждая группа преобразуется в соответствующий эквивалент.

$$\begin{array}{ccccccc}

& 3 & 2 & 6 & 6 & 4 & \\

& \swarrow & \swarrow & \swarrow & \swarrow & \swarrow & \\

11010110, 11010_2 = 011 & 010 & 110, 110 & 100_2 = 326,64_8 \\

D & 6 & D & 0 & & & \\

\swarrow & \swarrow & \swarrow & \swarrow & & & \\

1101 & 0110, 1101 & 0000_2 = D6, D_{16}

\end{array}$$

Преобразование шестнадцатеричных чисел в восьмеричные осуществляется с помощью промежуточного преобразования в двоичные числа.

$$\begin{array}{ccccccc}

& C & 9 & 1 & F & 3 & \\

& \swarrow & \swarrow & \swarrow & \swarrow & \swarrow & \\

C91,F3_{16} = 1100 & 1001 & 0001, 1111 & 0011 & 10 & = 6221,746_8 \\

\swarrow & \swarrow & \swarrow & \swarrow & \swarrow & & \\

6 & 2 & 2 & 1 & 7 & 4 & 6

\end{array}$$

Преобразуем в двоичный эквивалент, затем распределяем в группы по 3 бита и каждую группу записываем в восьмеричное число.

$$\begin{array}{ccccc}

& 7 & 5 & 1 & 4 & 2 \\

& \swarrow & \swarrow & \swarrow & \swarrow & \swarrow \\

751,42_8 = 000 & 111 & 101 & 001, 100 & 010 & 00 = 1E9,88_{16}

\end{array}$$

Преобразуем в двоичный эквивалент, затем распределяем в группы по 4 бита и каждую группу записываем в шестнадцатеричных числах.

### Преобразование чисел из десятичной системы счисления в двоичную, восьмеричную, шестнадцатеричную системы счисления

Преобразование десятичных чисел в двоичные, восьмеричные, шестнадцатеричные можно выполнять методом последовательного деления на 2, на 8, на 16 целой части числа с записью частного и остатка после каждого такого деления пока частное в целых числах не будет больше 0. Обратите внимание, что результат, полученный при записи первого остатка, записан будет на месте младшего разряда, а последний - на месте старшего.

|                     | Частное | Остаток             |

|---------------------|---------|---------------------|

| $177 \setminus 2 =$ | 88      | 1<br>Младший разряд |

| $88/2 =$            | 44      | 0                   |

| $44/2 =$            | 22      | 0                   |

| $22/2 =$            | 11      | 0                   |

| $11/2 =$            | 5       | 1                   |

| $5/2 =$             | 2       | 1                   |

| $2/2 =$             | 1       | 0<br>Старший разряд |

|           | Частное             | Остаток             |

|-----------|---------------------|---------------------|

| $177/8 =$ | 22                  | 1<br>Младший разряд |

| $22/8 =$  | 2<br>Старший разряд | 6                   |

$$177_{10} = 261_8$$

|            | Частное              | Остаток             |

|------------|----------------------|---------------------|

| $177/16 =$ | 11<br>Старший разряд | 1<br>Младший разряд |

11 соответствует знаку В

$$177_{10} = B1_{16}$$

$$177_{10} = 10110001_2 = 261_8 = B1_{16}$$

$$177,33_{10} = 10110001,01_2 = 261,25_8 = B1,54_{16}$$

При переводе дробной части десятичного числа выполняется умножение ее на основание новой системы счисления.

$$177,33_{10}$$

|    |      |

|----|------|

| 0, | 33·2 |

| 0  | 66·2 |

| 1  | 32·2 |

| 0  | 64   |

$$0,01_2$$

|    |      |

|----|------|

| 0, | 33·8 |

| 2  | 64·8 |

| 5  | 12·8 |

| 0  | 96   |

$$0,25_8$$

|    |       |

|----|-------|

| 0, | 33·16 |

| 5  | 28·16 |

| 4  | 88    |

$$0,54_{16}$$

## РАЗДЕЛ 2. ЛОГИЧЕСКИЕ ОСНОВЫ ЭВМ

### Тема 2.1. Основы теории переключательных функций

Логические функции и схемы. Способы представления логических функций: словарное, табличное, формульное, графическое. Условные графические обозначения (УГО) логических элементов. Основные законы и тождества алгебры логики. Понятие логического базиса. Базисы И-НЕ; ИЛИ-НЕ; И, ИЛИ, НЕ. Логические элементы ТТЛ, ТЛШ, ЭСЛ, МОП, КМОП, ИСЛ: схемы, параметры.

К элементарным логическим функциям относят функции: *инверсии, дизъюнкции и конъюнкции*.

**Инверсия (отрицание, операция НЕ).** Если есть некоторое высказывание  $X$ , то его отрицание *не X*.

| $X$ | $y = \bar{X}$ |

|-----|---------------|

| 0   | 1             |

| 1   | 0             |

Таким образом, если  $X=1$ , то  $\bar{X}=0$ , если  $X=0$ , то  $\bar{X}=1$ .

**Дизъюнкция (логическое сложение, операция ИЛИ).** Этую функцию принято обозначать символом  $\vee$ , например,  $x_1 \vee x_2$  и читать *икс один или икс два*. Функция может быть представлена таблицей истинности – табл. 1. Следует отметить, что данная операция справедлива для произвольного числа переменных, т.е.  $x_1 \vee x_2 \vee x_3 \vee x_4 \dots$ .

Таблица 1. Таблица истинности операции ИЛИ

| $x_1$ | $x_2$ | $x_1 \vee x_2$ |

|-------|-------|----------------|

| 0     | 0     | 0              |

| 0     | 1     | 1              |

| 1     | 0     | 1              |

| 1     | 1     | 1              |

Из табл. 1 следует, что функция принимает значение «1», если хотя бы один аргумент равен «1».

**Конъюнкция (логическое умножение, операция И).** Этую операцию обозначают символом  $\wedge$  или  $\&$ , например  $x_1 \wedge x_2$  и читается: *икс один и икс два*. Таблица истинности для операции И приведена в табл. 2. Правило логического умножения справедливо не только для двух сомножителей, но и для любого их количества, т.е.  $x_1 \wedge x_2 \wedge x_3 \wedge x_4 \dots$ .

Таблица 2. Таблица истинности операции «И»

| $x_1$ | $x_2$ | $x_1 \wedge x_2$ |

|-------|-------|------------------|

| 0     | 0     | 0                |

| 0     | 1     | 0                |

| 1     | 0     | 0                |

| 1     | 1     | 1                |

Из табл. 2 видно, что функция принимает значение «1», когда все переменные равны «1».

### Основные тождества и законы алгебры логики

На основе рассмотренных логических выражений можно записать любое сложное логическое выражение, т.е. любую логическую связь можно выразить посредством логических операций И, ИЛИ, НЕ.

Эти логические функции обладают рядом свойств, аналогичных свойствам обычной арифметики. Для них остаются справедливыми законы: сочетательный, распределительный и переместительный. Для дизъюнкции и конъюнкции справедливы следующие тождества – табл. 3

Таблица 3

| Тождества дизъюнкции | Тождества конъюнкции   |

|----------------------|------------------------|

| $x \vee x = x$       | $x \wedge x = x$       |

| $\bar{x} \vee x = 1$ | $\bar{x} \wedge x = 0$ |

| $x \vee 1 = 1$       | $x \wedge 1 = x$       |

| $x \vee 0 = x$       | $x \wedge 0 = 0$       |

Используя названные выше законы и тождества, нетрудно доказать справедливость следующих законов (2), (3):

$$x_1 \cdot x_2 \vee x_1 \cdot \overline{x_2} = x_1; \quad (x_1 \vee \overline{x_2}) \cdot (x_1 \vee x_2) = x_1 \quad \text{закон склеивания; (2)}$$

$$x_1 \vee x_1 \cdot x_2 = x_1; \quad x_1 \cdot (x_1 \vee x_2) = x_1 \quad \text{закон поглощения. (3)}$$

Правило де Моргана позволяет в логических выражениях произвести замену знаков дизъюнкции на знаки конъюнкции и наоборот (4):

$$\overline{x_1 \cdot x_2} = \overline{x_1} \vee \overline{x_2} \quad \text{и} \quad \overline{x_1 \vee x_2} = \overline{x_1} \cdot \overline{x_2} \quad (4)$$

Правило де Моргана справедливо для любого числа аргументов.

$$\bar{X} = X$$

**Закон двойного отрицания:**

|                                                                  |                                                                                   |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Перевод чисел в базис И-НЕ ,                                     | ИЛИ-Не                                                                            |

| $\underline{X_1 \cdot \bar{X}_3 \vee X_2 \cdot X_3 \cdot X_4} =$ | $(X_1 \vee X_3)(\bar{X}_2 \vee \bar{X}_3 \vee X_4)$                               |

| $\underline{X_1 \cdot \bar{X}_3 \vee X_2 \cdot X_3 \cdot X_4} =$ | $(X_1 \vee X_3) \cdot (\bar{X}_2 \vee \bar{X}_3 \vee X_4)$                        |

| $(X_1 \cdot \bar{X}_3) \cdot (X_2 \cdot X_3 \cdot X_4) =$        | $(X_1 \vee X_3) \vee (\bar{X}_2 \vee \bar{X}_3 \vee X_4)$                         |

| $(X_1 \mid \bar{X}_3) \mid (X_1 \mid X_3 \mid X_4)$              | $(X_1 \downarrow X_3) \downarrow (\bar{X}_2 \downarrow \bar{X}_3 \downarrow X_4)$ |

Помимо функций И, ИЛИ, НЕ есть еще несколько элементов функций, которые могут быть представлены через операции дизъюнкции и инверсии.

**Функция Шеффера** реализует логическое умножение с отрицанием (5):

$$x_1 | x_2 = \overline{x_1 \cdot x_2} \quad (5)$$

Эта функция имеет и другие названия: Штрих Шеффера, отрицание конъюнкции, И-НЕ. Функция принимает значение «1», если хотя бы один аргумент равен «0». Таблица истинности приведена в табл. 4.

**Функция Пирса** реализует логическое сложение с отрицанием:

$$x_1 \downarrow x_2 = \overline{x_1 \vee x_2} \quad (6)$$

Другие названия этой функции: Стрелка Пирса, отрицание дизъюнкции, ИЛИ-НЕ. Функция принимает значение «1», когда оба аргумента равны «0». Таблица истинности приведена в табл. 4.

**Функция, ИСКЛЮЧАЮЩЕЕ ИЛИ.** Другие названия этой функции: неравнозначность, сумма по модулю два. Функция принимает значение «1», когда аргументы неравны. Форма записи функции (7):

$$\overline{x_1 \oplus x_2} = \overline{x_1 x_2 \vee \bar{x}_1 \bar{x}_2} = (x_1 \vee x_2)(\bar{x}_1 \vee \bar{x}_2) \quad (7)$$

**Функция, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ.** Другие названия этой функции: равнозначность, эквивалентность. Функция принимает значение «1», когда аргументы равны. Форма записи функции (8):

$$\overline{x_1 \oplus x_2} = \overline{x_1 x_2 \vee \bar{x}_1 \bar{x}_2} = (x_1 \vee \bar{x}_2)(\bar{x}_1 \vee x_2) \quad (8)$$

Все приведенные функции могут быть записаны для любого количества аргументов.

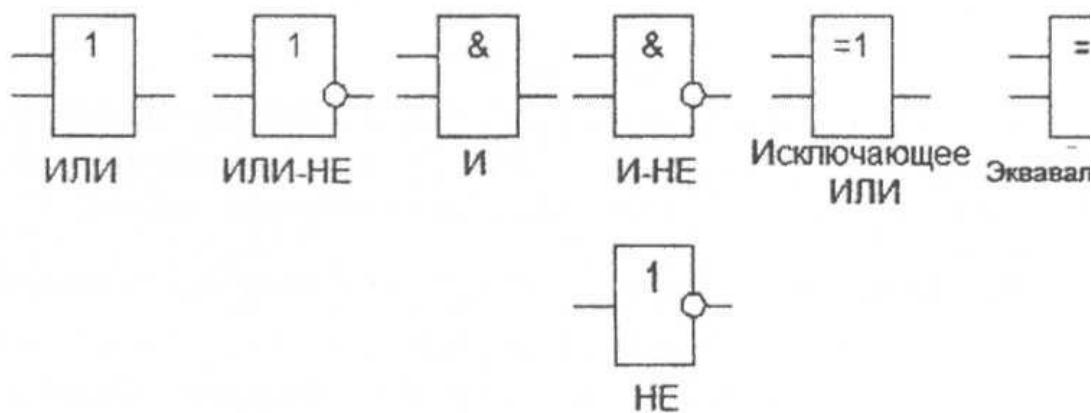

Табл. 4 является сводной таблицей истинности этих функций. На рис. 1 условное графическое обозначение (УГО) элементов, выполняющих эти функции.

Таблица 4. Таблицы истинности логических функций

| $x_1$ | $x_2$ | $x_1   x_2 = \overline{x_1 \cdot x_2}$ | $x_1 \downarrow x_2 = \overline{x_1 \vee x_2}$ | $x_1 \oplus x_2$ | $x_1 \oplus x_2$ |

|-------|-------|----------------------------------------|------------------------------------------------|------------------|------------------|

| 0     | 0     | 1                                      | 1                                              | 0                | 1                |

| 0     | 1     | 1                                      | 0                                              | 1                | 0                |

| 1     | 0     | 1                                      | 0                                              | 1                | 0                |

| 1     | 1     | 0                                      | 0                                              | 0                | 1                |

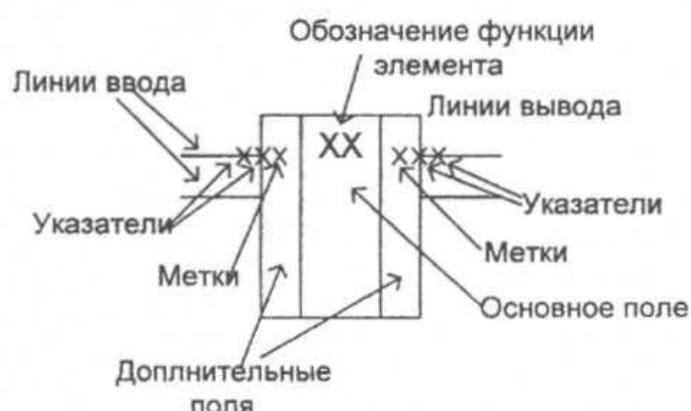

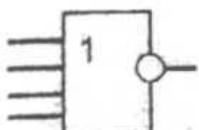

На рис. 2 приведено условное графическое обозначение рассмотренных элементов. Общие требования на условное графическое обозначение логических элементов и устройств устанавливает ГОСТ 2141-76 «Обозначения условные, графические в схемах. Элементы ци-техники» (Приложение А).

Рис. 2. УГО логических элементов

В результате изучения данной темы студент **должен знать**:

- способы задания логической функции;

- понятие таблицы истинности

- понятия - комбинационные и последовательностные устройства

- элементарные логические функции: И, ИЛИ, НЕ, И-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ЭКВИВАЛЕНТНОСТЬ, их таблицы истинности, обозначение на схемах, запись логических выражений через логические функции и через операции И, ИЛИ, НЕ;

- основные законы и тождества алгебры логики.

**Должен уметь**:

- записывать логические выражения с использованием операций И, ИЛИ, НЕ;

- преобразовывать логические выражения с использованием законов алгебры логики;

- выбирать базис для построения логических схем.

## Тема 2.2. Синтез логических устройств

Совершенная дизъюнктивная и конъюнктивная нормальные формы (СДНФ и СКНФ) представления функций. Комбинационные и последовательностные логические устройства, минимизация логических функций с помощью законов алгебры логики. Карты Карно. Диаграммы Вейча. Минимизация с помощью карт Карно (диаграмм Вейча). Анализ и синтез комбинационных логических устройств. Задачи анализа и синтеза. Переход от табличной формы представления логической функции к формульной. Этапы синтеза логических комбинационных устройств.

Основные параметры интегральных логических элементов. Классификация. Условное графическое обозначение (УГО) элементов цифровой техники (ГОСТ 2.743-91).

В качестве активных элементов современных цифровых микросхем в настоящее время применяются транзисторы: биполярные и полевые. Способ соединения транзисторов между собой в пределах одного элемента определяет их логический базис или, иначе, логику. Цифровые микросхемы на биполярных транзисторах существенно отличаются по многим показателям и здесь выделяют несколько разновидностей: ТТЛ - транзисторно-транзисторная логика, ТТЛШ - транзисторно-транзисторная логика с диодами Шотки, АС - перспективные сверхскоростные с переходом Шотки, ЭСЛ - эмиттерно-связанная логика, ИИЛ (ИИ<sup>2</sup>) - интегральная инжекционная логика и др.

Микросхемы на основе полевых транзисторов также широко используются в настоящее время. Здесь различают: *n*-МОП - логика - в качестве активного элемента используется транзистор с каналом *n*-типа; *p*-МОП - логика - в качестве активного элемента используется транзистор с каналом *p*-типа; КМОП - логика комплементарная металл-окисел - полупроводниковая транзисторная логика. Комплементарной называют пару транзисторов, сходных по абсолютным значениям параметров, но с полупроводниковыми структурами, взаимно отображенными как в виде негатива так и позитива, т.е. в совместную работу включены одновременно транзисторы с каналом *n* - типа и *p* - типа.

В настоящее время широко применяются микросхемы транзисторно-транзисторной логики. Принцип действия различных модификаций ТТЛ одинаков и различаются они типом корпуса, временем задержки и потребляемой мощностью. Основные электрические параметры для всех серий ТТЛ согласованы, благодаря чему, микросхемы, относящиеся к разным сериям, могут непосредственно соединяться друг с другом.

Типовые значения параметров стандартной ТТЛ приведены в табл. 5.

Таблица 5. Основные параметры стандартной ТТЛ

| Параметр                               | Значение параметра |

|----------------------------------------|--------------------|

| Напряжение питания, В                  | $5 \pm 5\%$        |

| Уровень логической единицы ( $U^1$ ) В | $\geq 2,4$         |

| Уровень логического нуля ( $U^0$ ) В   | $\leq 0,4$         |

| $I_{bx}^0$ , мА                        | $\leq -1,6$        |

| $I_{bx}^1$ , мА                        | $\leq 0,04$        |

| $t_{зд нс}^{0,1}$                      | $\leq 15$          |

| $t_{зд нс}^{1,0}$                      | $\leq 22$          |

| $K_{раз}$                              | 10                 |

| $P$ пот, мВт                           | $\leq 22$          |

| $f$ , МГц                              | $\leq 10$          |

Микросхемы выпускаются в виде серий, к которым относится ряд типов микросхем с различным функциональным назначением, имеющие единое КТ исполнение и предназначенные для совместного использования.

Тип микросхемы указывает на конкретное функциональное назначение и определенные конструктивно-технологические и схемо-технические решения. Каждый тип микросхемы имеет свое условное обозначение, которое состоит из шести элементов.

Система условных обозначений (маркировка) микросхем для устройств широкого применения состоит из шести элементов.

**Пример:** К М 5 30 ЛП 5

1 2 3 4 5 6

**Первый элемент.** Буква «К» показывает, что микросхема предназначена для широкого применения

**Второй элемент.** Буква «М» - характеристика материала и типа корпуса. В данном случае М – металлокерамический.

**Третий элемент.**

1,5,6,7 – полупроводниковые;

2,4,8 - гибридные;

2 – прочие.

**Четвертый элемент.** Две или три цифры – порядковый номер разработки серии. Вместе 3-й и 4-й элементы обозначают номер конкретной серии - 530.

**Пятый элемент.** Две буквы – Функциональное назначение микросхемы. В зависимости от выполняемых функций микросхемы подразделяется на подгруппы (генераторы, триггеры, усилители) и виды (преобразователи длительности, напряжения, частотный).

**Шестой элемент.** Цифра 6 – порядковый номер разработки в конкретной серии (среди микросхем одного вида). Следующие две буквы от А до Я показывают на разбраковку (допуск на разброс) по электрическим параметрам.

Микросхема представляет собой четыре двухходовых элемента ИСключающее ИЛИ. Содержат 176 интегральных элементов. Корпус типа 401.14-5, масса не более 0,65г и типа 201.14-10, масса не более 1,6г

**Пятый элемент маркировки представлен в табл. в приложении А**

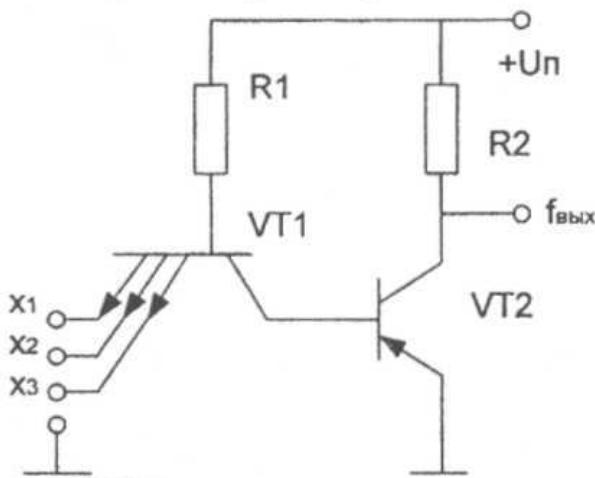

Простейшее схемотехническое решение базового элемента транзисторно-транзисторной логики приведено на рис. 3.

Многоэмиттерный транзистор VT1 выполняет функцию И, транзистор VT2 является инвертором. Схема стандартного элемента И-НЕ ТТЛ в действительности несколько сложнее. Это делается для повышения быстродействия, помехоустойчивости и нагрузочной способности, но принцип работы остается тем же.

**Быстродействие** характеризуется максимальной частотой смены входных сигналов, при которой еще не нарушается нормальное функционирование. Этот параметр определяет время обработки информации.

**Помехоустойчивость** определяет допустимое напряжение помех на входах микросхемы. Этот параметр оценивается по нескольким показателям. В зависимости от продолжительности помехи различают статическую и динамическую помехоустойчивость. Статическую помехоустойчивость связывают с помехами, длительность которых больше времени переходных процессов, а динамическую – с кратковременными помехами.

Рис. 3. Элемент И-НЕ транзисторно-транзисторной логики

**Коэффициент разветвления** (нагрузочная способность) –  $K_{раз}$  – определяет максимальное число входов элементов данной серии, которым можно нагружать выходы микросхемы без нарушения ее нормального функционирования.

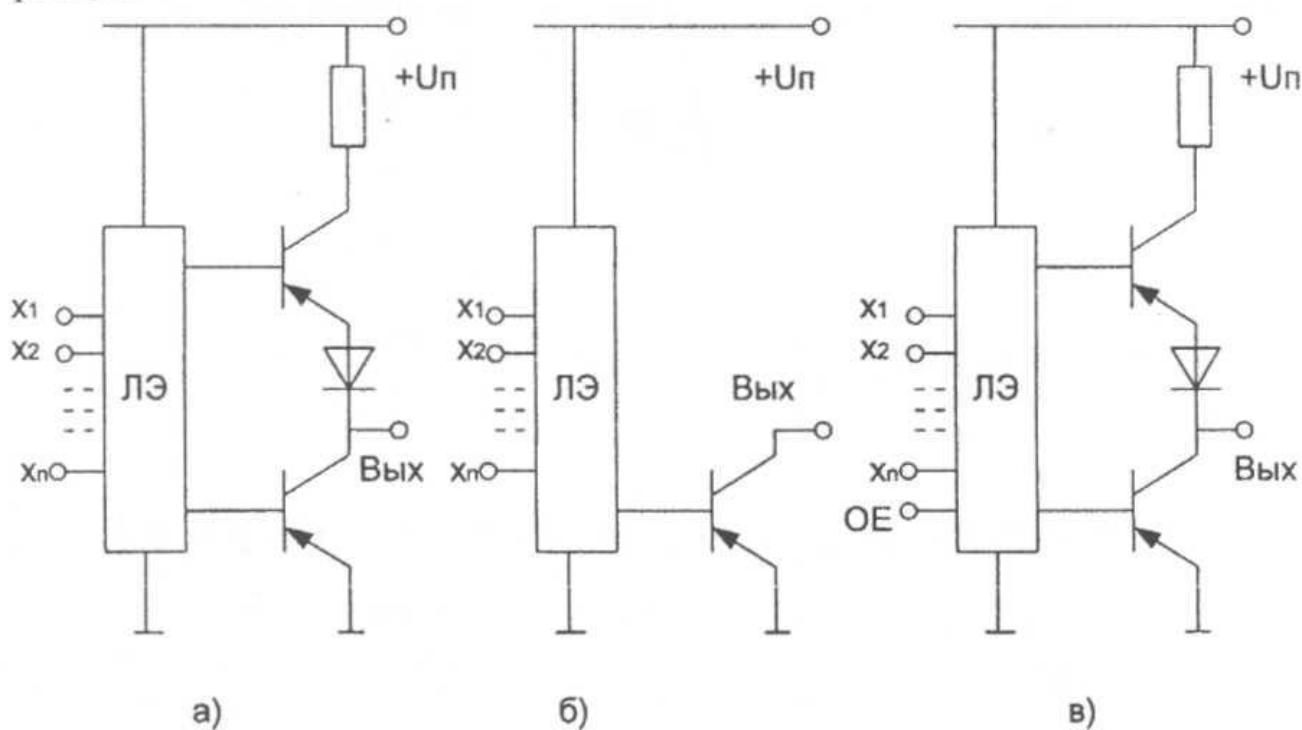

Физические параметры и функциональные возможности логического элемента (ЛЭ) зависят от способа схемной реализации выходного каскада. Наиболее часто используются пять типов схем выходных каскадов.

Наиболее часто используются ЛЭ со стандартным выходом рис. 4а. Этот выходной каскад в различных сериях может иметь различные модификации. ЛЭ со стандартным выходом имеют нагрузочную способность  $K_{\text{раз}} = 10$  (для некоторых серий это значение может быть иным). Такой же выходной каскад имеют ЛЭ с повышенной нагрузочной способностью. Обычно для них  $K_{\text{раз}} = 30$ . На УГО в этом случае проставляется специальный символ (рис. 5а).

В логических элементах с *открытым коллектором* (рис. 4б) в качестве выходного каскада используется транзистор, коллектор которого не подключен к нагрузке. Эти транзисторы изготавливаются на разное допустимое напряжение питания. Выходы таких ЛЭ должны подключаться с помощью внешнего резистора к источнику питания. На УГО для таких элементов проставляется символ – рис. 5б.

Выходной каскад с *открытым эмиттером* отличается от выходного каскада с открытым коллектором тем, что эмиттер не подключен внутри ИС к общему выводу, а подключен кциальному внешнему выводу. Коллектор подключен к шине питания. Нагрузку подключают между выводом эмиттера и корпусом. На УГО проставляется символ – рис. 5в.

На рис. 4в показан ЛЭ с *тремя состояниями*. Такие логические элементы имеют дополнительный вход управления ОЕ. Когда на этом входе устанавливается активное значение сигнала, то оба транзистора переходят в закрытое состояние, и, таким образом, выход отключается от корпуса и источника питания. Для обозначения такого выхода на УГО ставится символ – рис. 5г.

Рис. 4. Типы выходных каскадов

Если у выбранных элементов остаются свободными входы, то они должны быть задействованы. Эти входы надо соединить с работающими или подать на них постоянное напряжение, соответствующее уровням логического нуля ( $U^0$ ) или логической единицы ( $U^1$ ), в зависимости от логики работы.

Рис. 5. Символы, обозначающие тип выхода

Большое распространение получили в последнее время интегральные микросхемы на основе полевых транзисторов структуры МОП. Принципиальные особенности транзисторов этого вида позволяют создавать элементы и целые цифровые устройства с малым потреблением мощности при высокой помехоустойчивости и нагрузочной способности. Сравнительно с биполярными транзисторами они имеют меньшие размеры, что позволяет разместить на единице площади кристалла большее число элементов. Базовыми элементами для различных функциональных узлов КМОП-структур являются инвертор и двунаправленный тактируемый ключ. Эти элементы состоят только из МОП-транзисторов с каналами обоих видов проводимости и не содержат резисторов и конденсаторов.

В качестве примера в табл. 6 приведены параметры микросхем серии К176, структура которых реализована по КМОП - технологии.

Таблица 6. Основные параметры базовых ЛЭ серии К176

| Параметр                               | Значение параметра |

|----------------------------------------|--------------------|

| Напряжение питания, В                  | $9 \pm 5\%$        |

| Уровень логической единицы ( $U^1$ ) В | $\geq 8,2$         |

| Уровень логического нуля ( $U^0$ ) В   | $\leq 0,3$         |

| $I_{\text{вх}}^0, \text{ мА}$          | $\leq 1,0$         |

| $I_{\text{вх}}^1, \text{ мА}$          | $\leq 1,0$         |

| $t_{\text{зд}}^{0,1} \text{ нс}$       | $\leq 200$         |

| $t_{\text{зд}}^{1,0} \text{ нс}$       | $\leq 200$         |

| $K_{\text{раз}}$                       | 50                 |

| $P_{\text{пот}}, \text{ мВт}$          | $\leq 10$          |

| $f, \text{ МГц}$                       | $\leq 10$          |

## РАЗДЕЛ 3. ТИПОВЫЕ УЗЛЫ ЭВМ

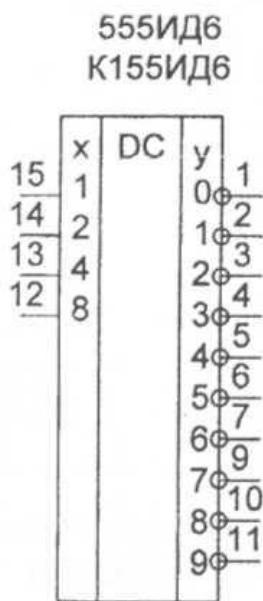

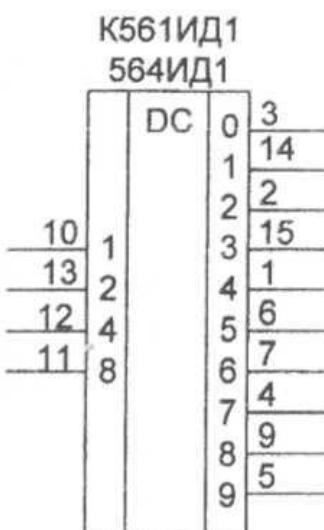

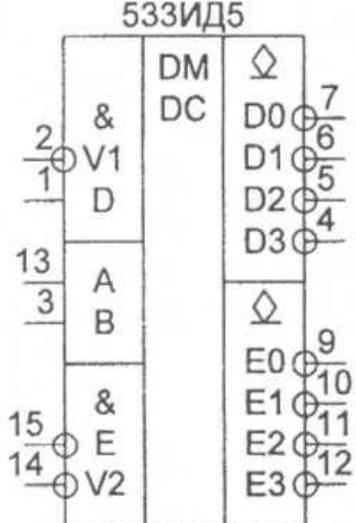

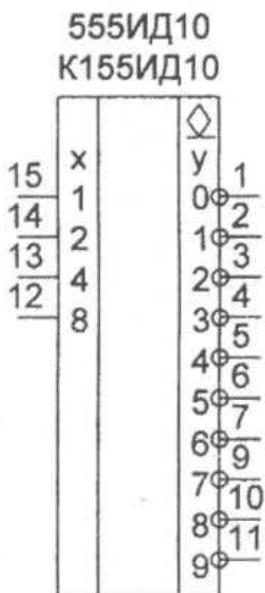

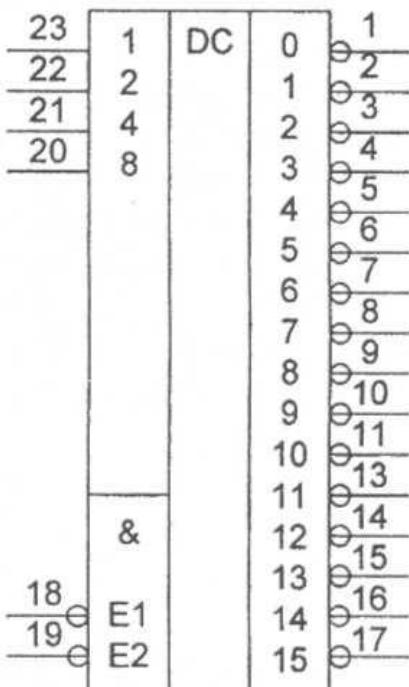

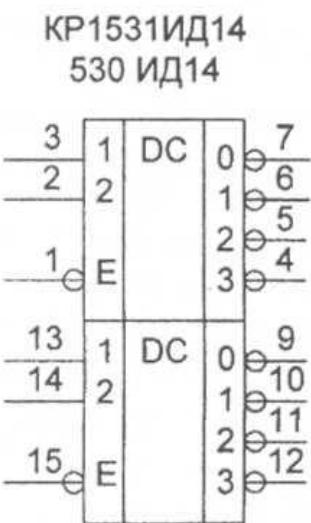

### **Тема 3.1. Шифраторы и дешифраторы**

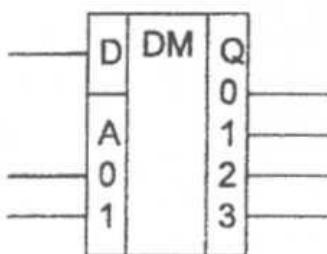

Назначение шифраторов. Синтез шифраторов на интегральных схемах. Назначение и классификация дешифраторов. Синтез линейного дешифратора. Каскадные, матричные дешифраторы. Дешифраторы в интегральном исполнении. УГО. Сравнительный анализ различных дешифраторов, области использования.

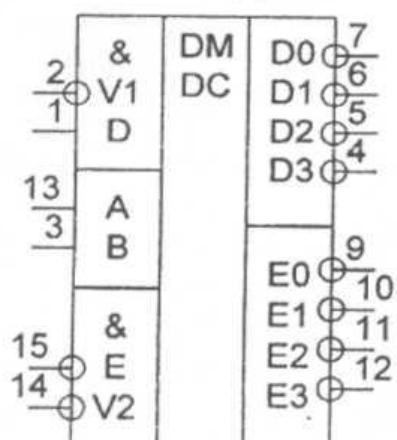

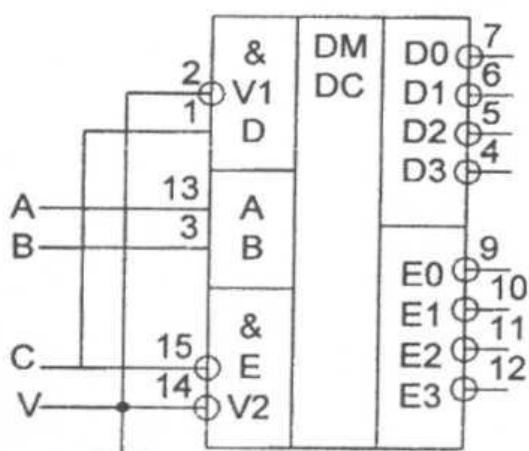

### **Тема 3.2. Мультиплексоры и демультиплексоры**

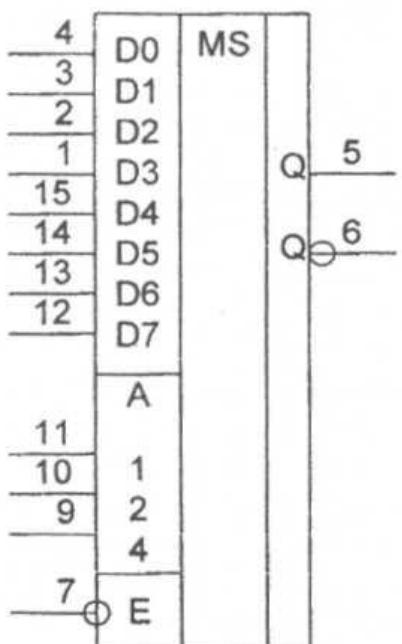

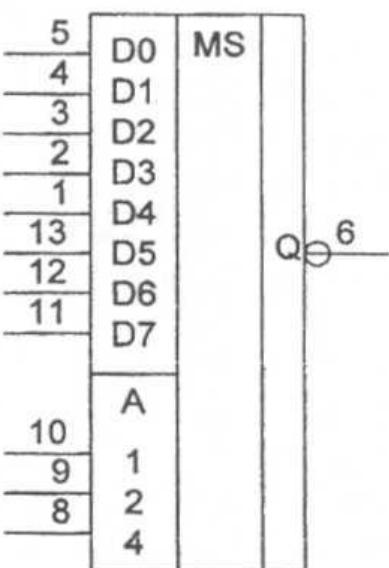

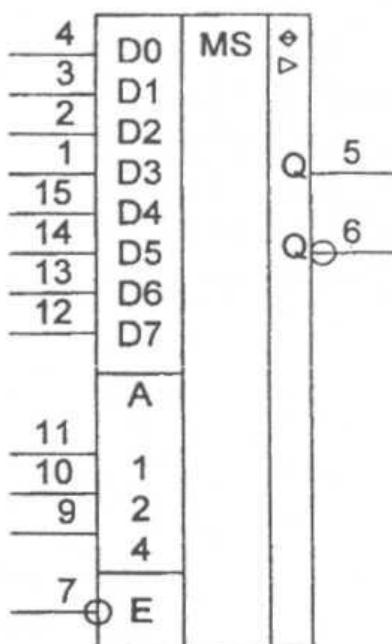

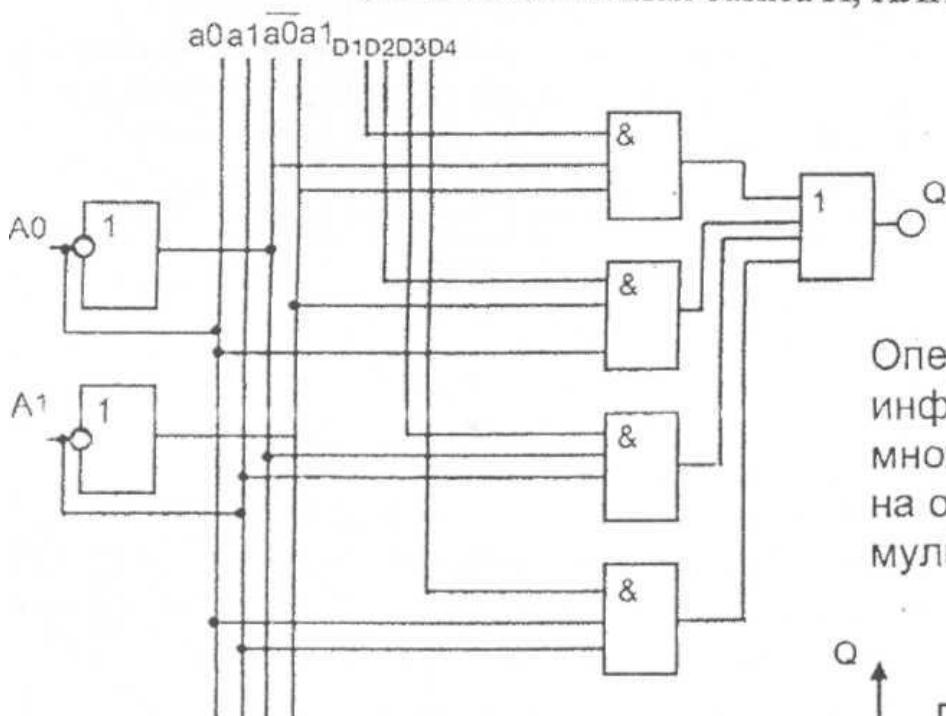

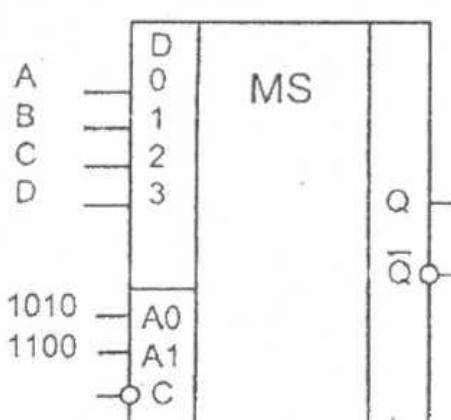

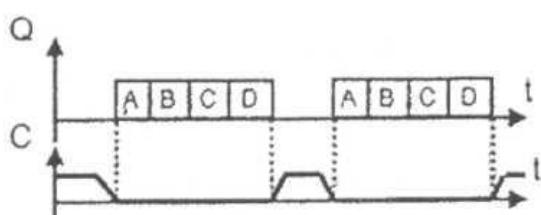

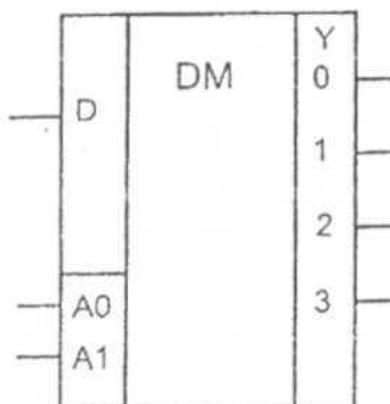

Назначение мультиплексоров. Схема мультиплексора, УГО. Мультиплексоры в интегральном исполнении, способы наращивания. Универсальность мультиплексоров. Назначение демультиплексоров. Схема демультиплексора. УГО. Демультиплексоры в интегральном исполнении. Электронный коммутатор.

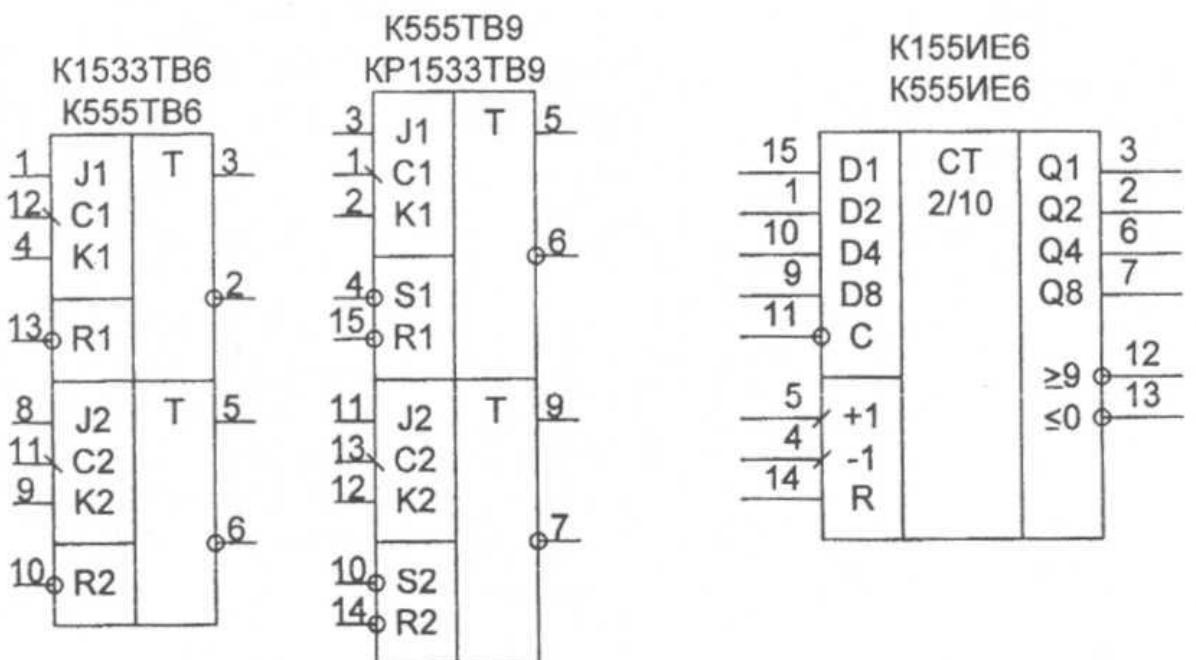

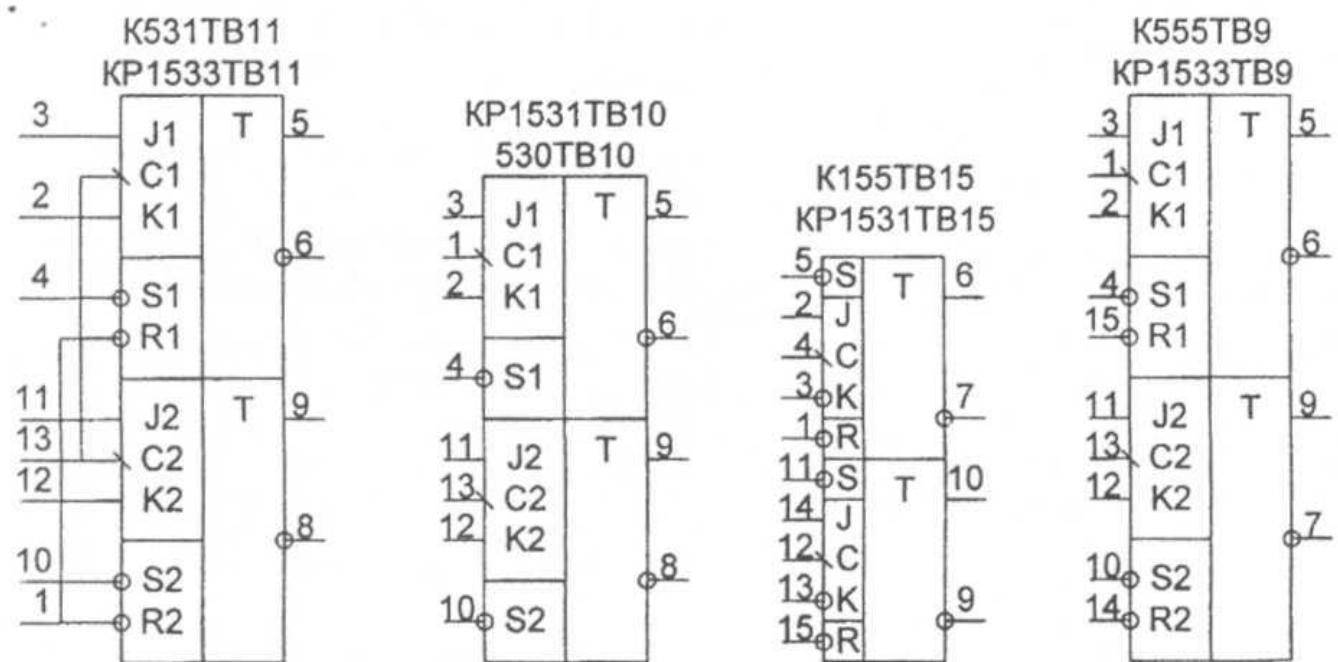

### **Тема 3.3. Триггеры в интегральном исполнении**

Типы триггеров. Таблицы переключения R-S триггера, D-триггера, T-триггера. J-K-триггера. Временные диаграммы.

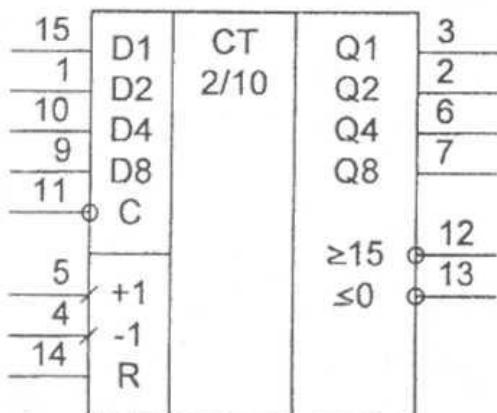

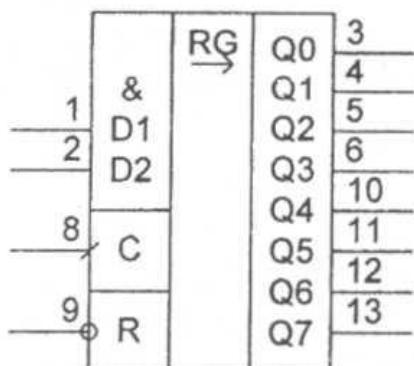

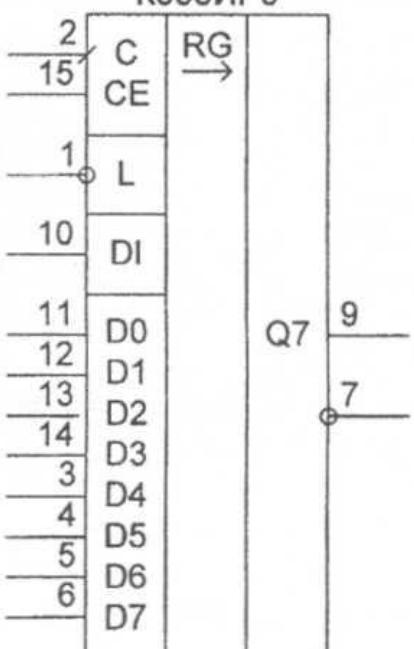

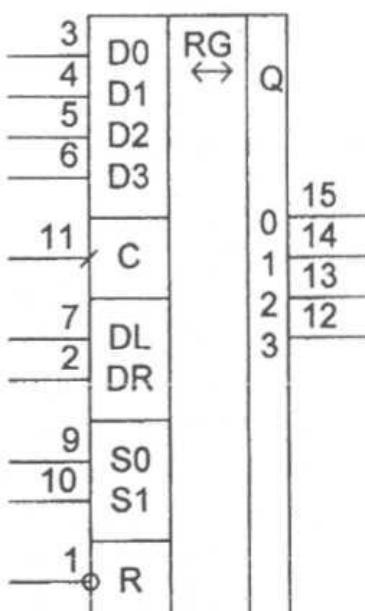

### **Тема 3.4 Регистры**

Назначение, классификация, характеристики регистров. Схемы параллельного, сдвига, реверсивного регистров УГО. Схема выдачи информации. Регистры в интегральном исполнении.

### **Тема 3.5. Счетчики**

Назначение, классификация, характеристики счетчиков. УГО. Схемы асинхронных и синхронных счетчиков; с последовательным, сквозным, параллельным переносом. Счетчики с произвольным коэффициентом пересчета. Счетчики в интегральном исполнении и их использование в качестве делителей частоты. Кольцевые счетчики.

### **Тема 3.6 Сумматоры**

Назначение, классификация и характеристики. УГО. Математическое описание и схема одноразрядного полного комбинационного сумматора. Многоразрядные сумматоры: параллельные и последовательные. Организация ускоренного переноса. Сумматоры в интегральном исполнении.

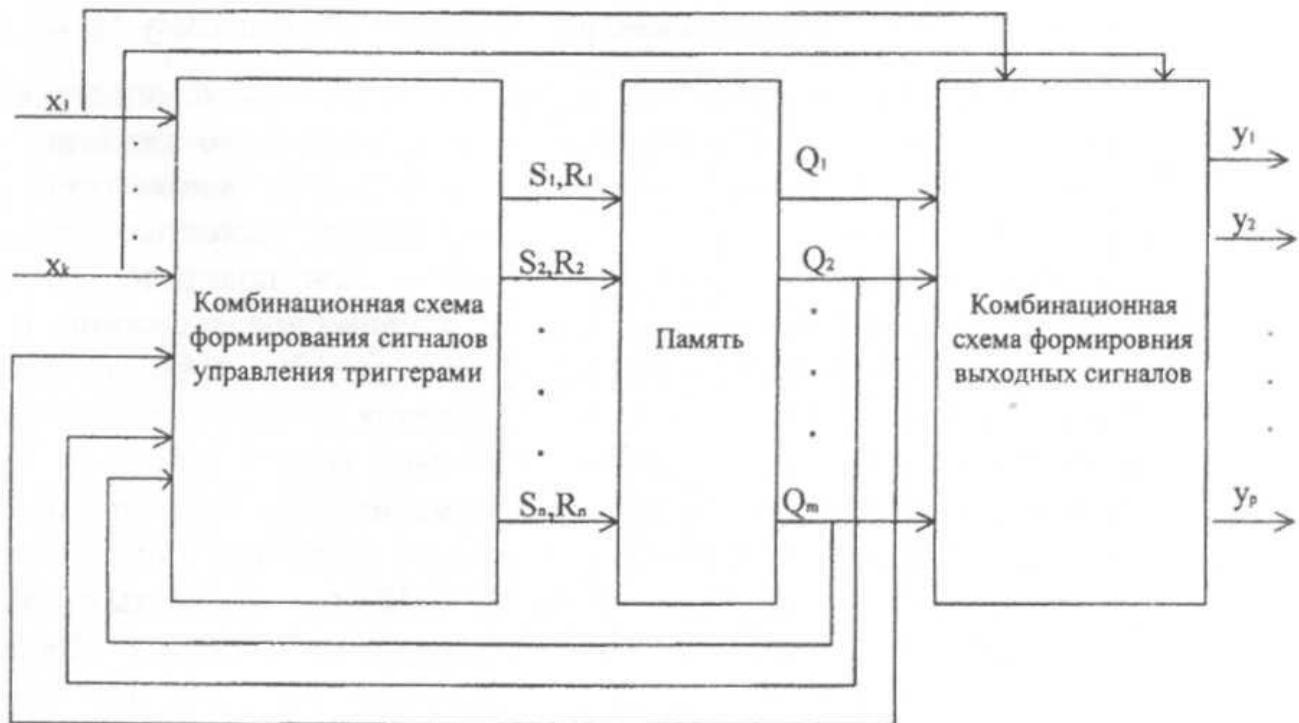

В зависимости от элементов, входящих в состав цифрового устройства, все они делятся на два типа: комбинационные и последовательностные.

Комбинационные устройства не содержат элементов памяти, и сигналы на выходах зависят только от входных сигналов, действующих в данный момент времени.

Последовательностные устройства содержат элементы памяти, и выходные сигналы зависят не только от входных, действующих в данный момент времени, но и от тех, которые действовали на входе раньше. Действие этих сигналов устройство запоминает и использует при формировании текущих выходных сигналов.

При разработке схем комбинационных логических устройств (КЛУ) целесообразно придерживаться следующих правил:

- на основании определения составить таблицу состояний устройства;

- записать на основе анализа таблицы состояний логические выражения и упростить их. На данном этапе в некоторых случаях удобно использовать карты Карно;

- привести полученные функции к заданному базису. Для этого следует применить закон двойного отрицания и теорему де Моргана;

- построить схему в заданном базисе.

К комбинационным цифровым устройствам относятся: шифраторы, дешифраторы, мультиплексоры, демультиплексоры, сумматоры, компараторы кодов и некоторые другие.

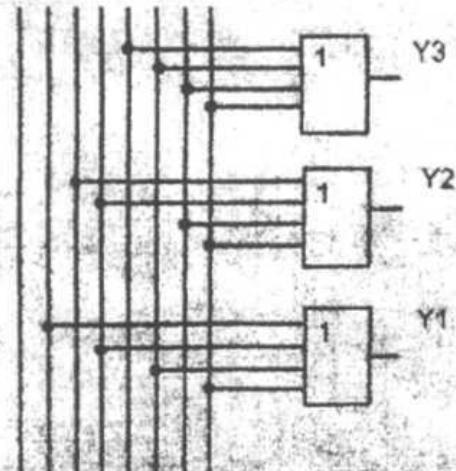

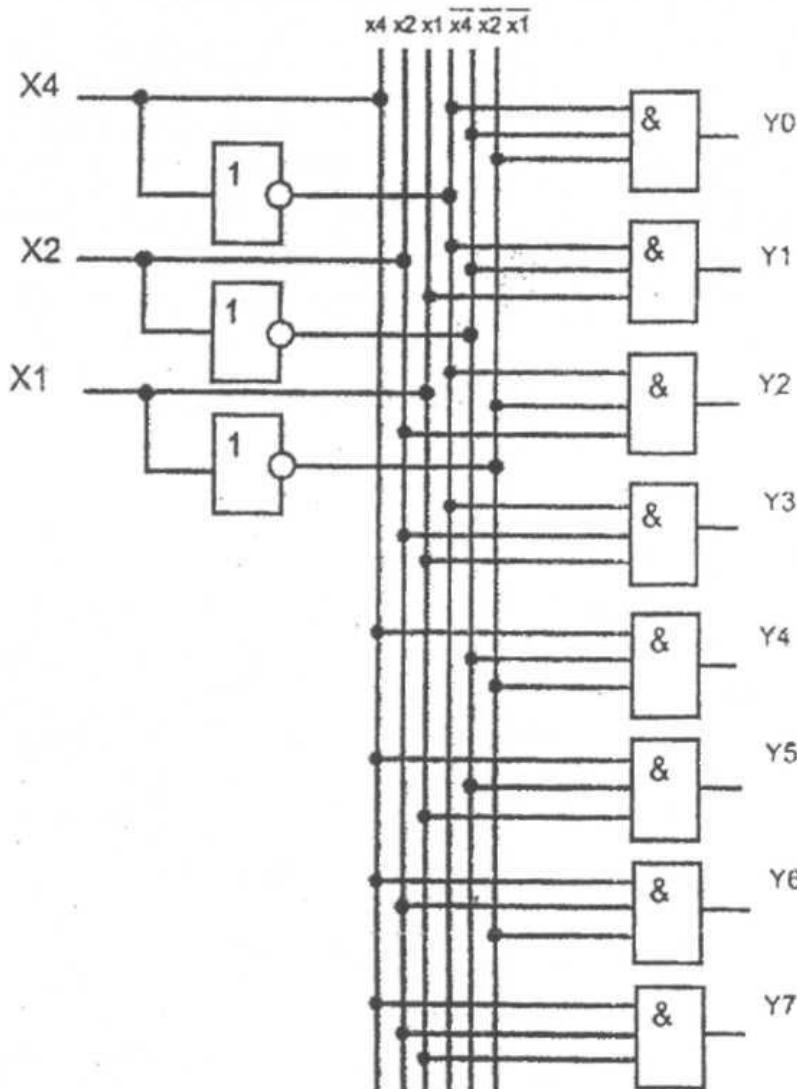

**Шифратором** называется комбинационное логическое устройство, преобразующее активный сигнал, действующий на одном из  $m$  входов в  $n$ -разрядный двоичный код. Активный сигнал действует только на одном из входов, а на всех остальных установлен пассивный уровень. Такой вход называют возбужденным. Например, если активным сигналом является логическая единица, то на всех других входах действует логический ноль (такой код называют унитарным). На выходе может формироваться любой двоичный код, в зависимости от того, как будет задана таблица состояний шифратора.

Число входов и выходов шифратора связано соотношением  $m=2^n$ . Например, возможны шифраторы типа  $8 \times 3$ , т.е. у шифратора восемь входов и три выхода;  $16 \times 4$  - шестнадцать входов и четыре выхода. Если каждому входу шифратора поставить в соответствие некоторое десятичное число, а на выходе будет формироваться двоичное число в коде 8-4-2-1, то можно считать, что данный шифратор преобразует десятичное число в двоичную систему счисления. Этот случай является частным, и нельзя его приводить для общего описания шифратора. В таком шифраторе не выполняется условия соотношения входов и выходов, т.е. будет  $m < 2^n$ .

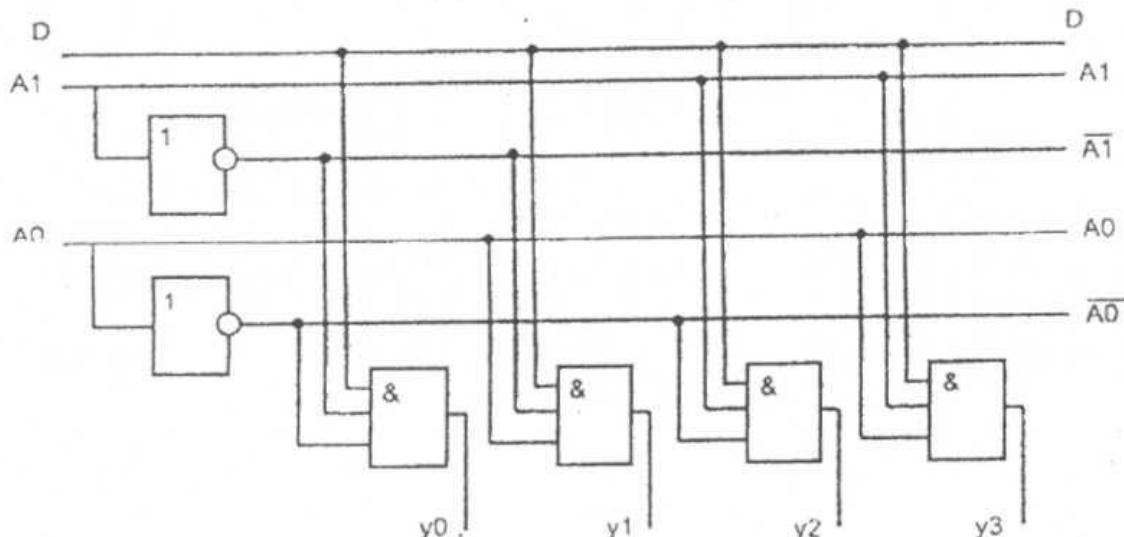

**Дешифратором** или декодером называется устройство, преобразующее двоичный код в унитарный (код *1 из m*). Из всех  $m$  выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого соответствует поданному на вход двоичному числу. На всех остальных выходах дешифратора уровни напряжения неактивные. Дешифратор обеспечивает возможность распознавания кодовых комбинаций и выполняет функцию обратную шифратору.

В зависимости от соотношения входов и выходов различают **декодаторы полные и неполные**. Если выполняется условие  $m=2^n$ , где  $m$  – число входов, а  $n$  – число выходов, т.е. используются все возможные наборы входных переменных, то такой дешифратор называется полным. В неполном дешифраторе используется лишь часть возможных наборов и меньше выходов. Примерами полных дешифраторов являются дешифраторы  $3 \times 8$ ,  $4 \times 16$ ,  $5 \times 32$  и т. д. Из неполных дешифраторов наиболее часто

используется дешифратор  $4 \times 10$ . Если определено условие, что на вход подается двоичный код 8-4-2-1, а каждому выходу дешифратора поставлено в соответствие определенное десятичное число, то можно считать - дешифратор преобразует двоичную систему счисления в десятичную. Это определение является частным и не может быть использовано для определения дешифратора в целом.

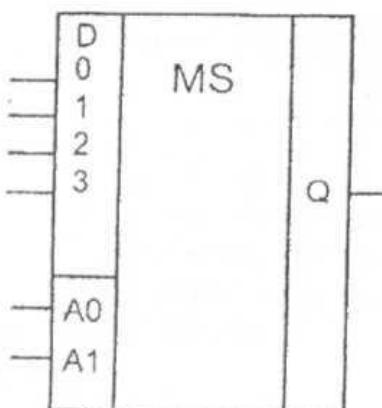

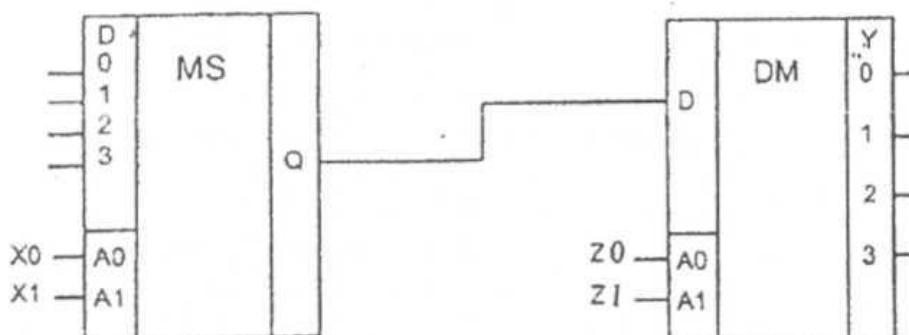

**Мультиплексор** это КЛУ, имеющий  $n$  входов данных, один выход и  $m$  адресных входов. Число входов данных и управляющих (адресных) входов связаны между собой отношением:  $m = \log_2 n$ . Таким образом, мультиплексор позволяет в произвольном порядке коммутировать поступающую с нескольких входных шин информацию на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор можно уподобить бесконтактному многопозиционному переключателю.

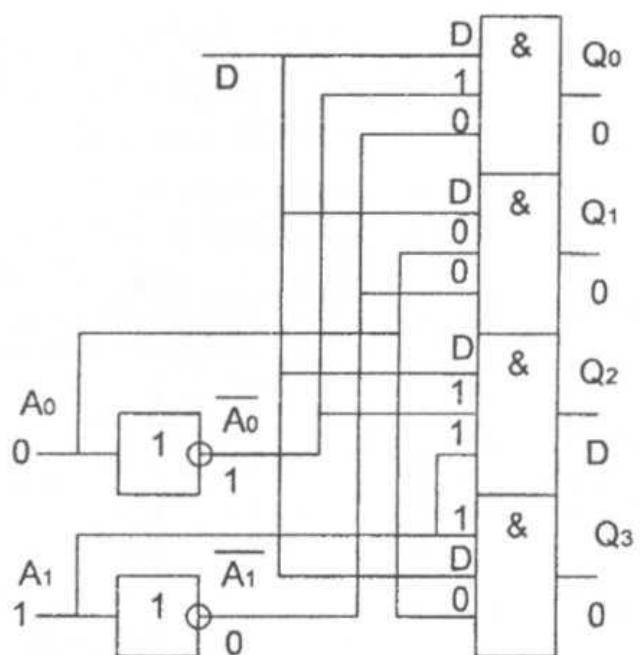

**Демультиплексором** называется КЛУ, предназначенное для управляемой передачи данных от одного источника информации к одному из нескольких выходных каналов. Согласно этому определению, демультиплексор в общем случае имеет один информационный вход,  $m$  адресных входов и  $n$  выходов. Количество адресных входов и информационных выходов связаны между собой соотношением:  $n = 2^m$ .

**Сумматором** называется логическое устройство, выполняющее арифметическую операцию сложения. Сумматоры, выполненные в виде самостоятельных микросхем, бывают только комбинационного типа. Различают полусумматоры, полные сумматоры и многоразрядные сумматоры.

**Полусумматор** – простейший суммирующий элемент, выполняющий сложение двух одноразрядных чисел и формирующий результат сложения и перенос.

Полный сумматор позволяет выполнить сложение трех одноразрядных чисел, что позволяет производить сложение с учетом переноса.

Многоразрядные сумматоры выполняют операцию сложения многоразрядных чисел. В таких сумматорах полные сумматоры по входам переноса соединяются последовательно, а разряды данных на вход поступают параллельно. Однако окончательный результат формируется некоторой задержкой, вызванной передачей сигнала переноса между разрядами. На вход переноса первого полусумматора подается логический ноль.

Правила арифметики во всех позиционных системах аналогичны. Основной операцией, которая используется в цифровых устройствах при выполнении различных арифметических действий, является операция сложения. Вычитание легко сводится к операции сложения путем замены вычитаемого дополнительным кодом. Операции умножения и деления также приводятся к операции сложения с использованием некоторых логических действий.

Рассмотрим пример сложения двух многоразрядных чисел:

$$A=11001011, \quad B=10011010.$$

Найдем  $S=A+B$ .

|                                                                                                           |                                                               |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| $  \begin{array}{r}  1\ 00110100 \\  + 11001011 \\  \hline  10011010 \\  \hline  01100101  \end{array}  $ | переносы<br>первое слагаемое<br>второе слагаемое<br>результат |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

Цифровое устройство может выполнять действия только над числами определенной разрядности, поэтому перенос, который образовался при сложении старших разрядов, теряется. Он не входит в результат. При необходимости сохранить его значение к сумматору подключают дополнительные устройства, например, триггеры, или увеличивают его разрядность.

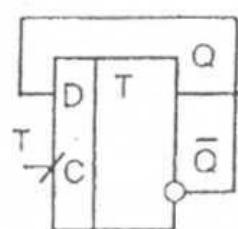

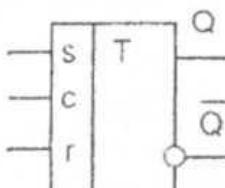

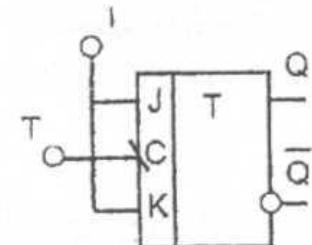

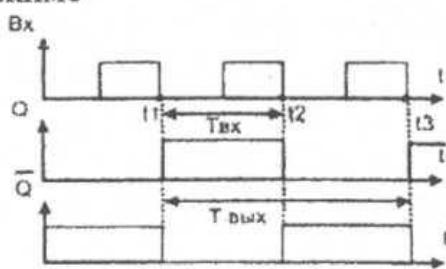

**Триггером** называется простейшее последовательностное устройство, которое может находиться в одном из двух устойчивых состояний и переходить из одного состояния в другое под воздействием входных сигналов. Состояние триггера определяется по сигналу на прямом выходе.

Для обозначения типа входа используются буквенные символы:

R - вход раздельной установки триггера в состояние 0;

S - вход раздельной установки триггера в состояние 1;

D - вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

T - счетный вход;

J - вход установки универсального триггера в состояние 1;

K - вход установки универсального триггера в состояние 0;

C - управляющий вход (вход синхронизации).

Для обозначения вида активного сигнала, под действием которого триггер может изменить свое состояние, используются графические символы (табл. 7).

Таблица 7. Свойства выводов

| Наименование                                                                                                            | Обозначение |

|-------------------------------------------------------------------------------------------------------------------------|-------------|

| Прямой статический вход.<br>Триггер переключается в период действия на входе уровня логической единицы.                 |             |

| Инверсный статический вход.<br>Триггер переключается в период действия на входе уровня логического нуля.                |             |

| Прямой динамический вход.<br>Триггер переключается, если сигнал на входе изменился из состояния "0" в состояние "1".    |             |

| Инверсный динамический вход.<br>Триггер переключается, если сигнал на входе изменился из состояния "1" в состояние "0". |             |

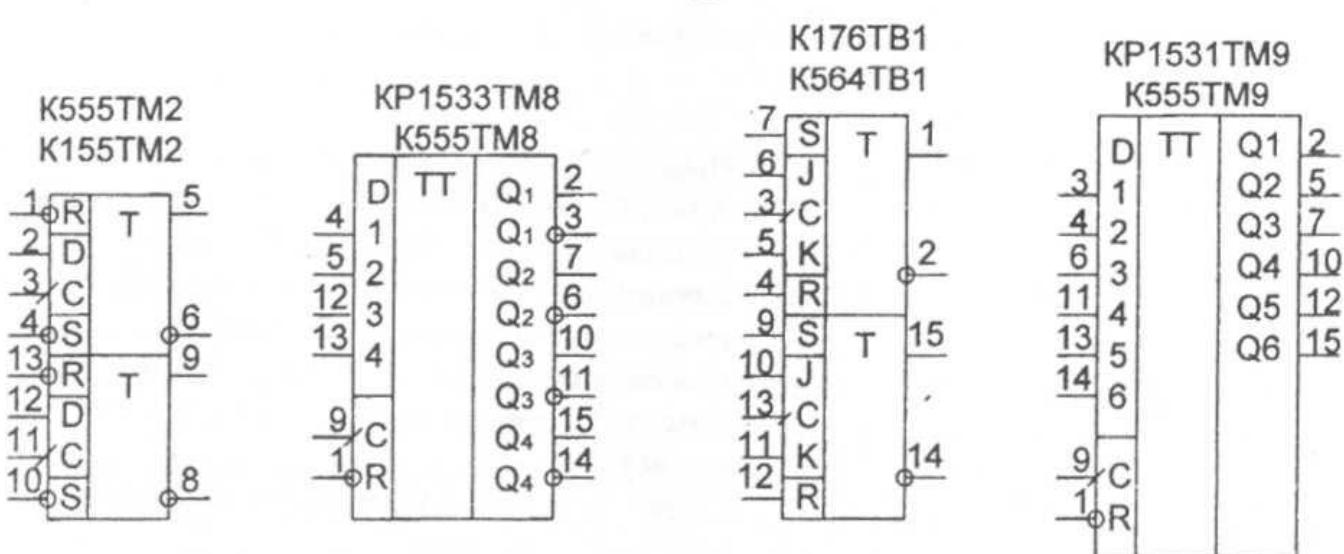

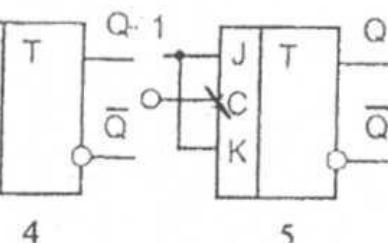

*Регистром* называется последовательностное цифровое устройство предназначенное для приема, хранения и выдачи информации. В зависимости от схемного построения регистры могут выполнять некоторые дополнительные функции: сдвигать записанное число вправо (в сторону младшего разряда) или влево (в сторону старшего разряда), преобразовывать последовательный код в параллельный и, наоборот, прямой код преобразовывать в обратный и др.

По способу приема и выдачи информации регистры подразделяют на:

- **параллельные**, в которых информация записывается и считывается только в параллельной форме;

- **последовательные**, в которых информация записывается и считывается только в последовательной форме;

- **последовательно-параллельные**, в которых информация записывается в последовательной форме, а выдается - в параллельной;

- **параллельно-последовательные**, в которых информация записывается в параллельной форме, а выдается - в последовательной.

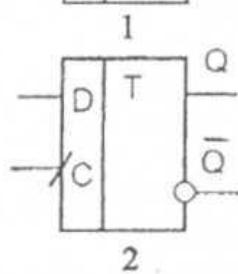

Элементами структуры регистров являются синхронные D-триггеры, RS- или JK-триггеры с динамическим или статическим управлением. Одиночный триггер может запоминать один бит (один двоичный разряд) информации. Поэтому для построения регистров в зависимости от назначения используют наборы или цепочки триггеров – по количеству разрядов числа.

Регистры, выпускаемые в виде интегральных микросхем, часто могут выполнять несколько функций. В этом случае их называют **комбинированными**. Интегральные регистры обычно бывают четырех-, восьми- и шестнадцатиразрядными.

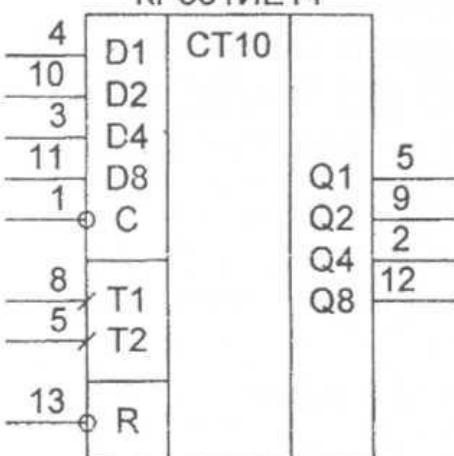

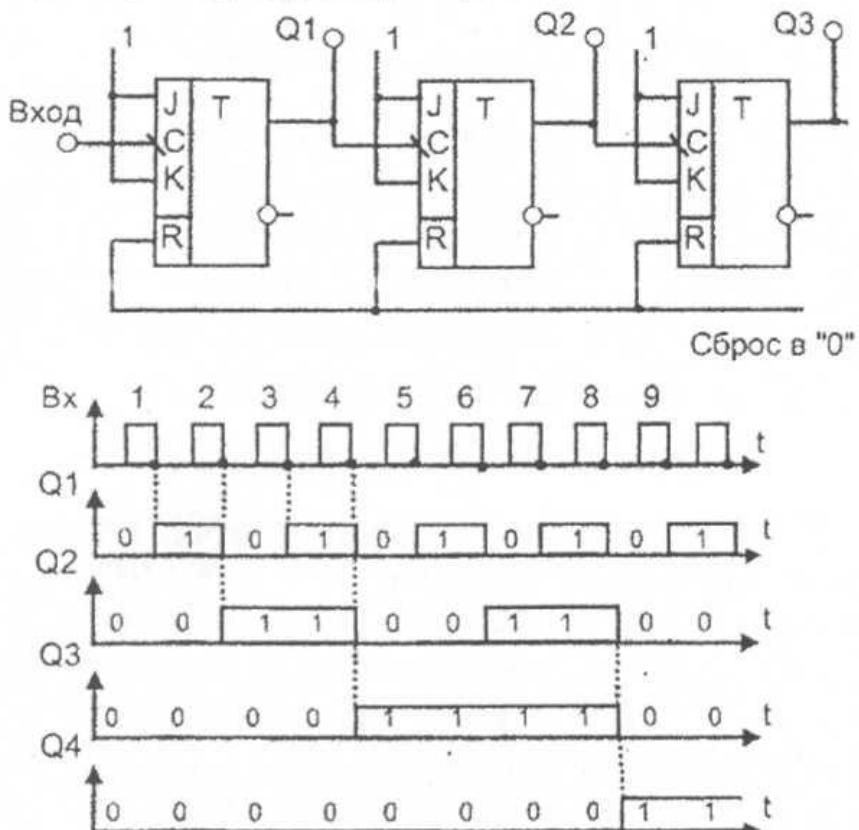

**Счетчиком** называется последовательностное цифровое устройство, сигналы, на выходе которого, в определенном коде отображают число импульсов, поступивших на счетный вход. Счетчики строятся на основе счетных триггеров, и цепочка из  $n$  триггеров сможет подсчитать в двоичном коде  $2^n$  импульсов. Каждый триггер такой цепочки является разрядом счетчика. Количество состояний, которые могут быть зафиксированы в счетчике, называется коэффициентом (модулем) счета -  $K_{сч}$ .

Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом. Остальные нумеруются по числу поступивших импульсов. Если число входных импульсов превышает коэффициент счета, то происходит переполнение, счетчик возвращается в начальное состояние и повторяется цикл работы. Например, в счетчике с  $K_{сч}=8$  зафиксировано число 5. Это значит, на его вход могло поступить 5, 13, 21, 29 и т.д. импульсов. В общем случае состояние счетчика определяется по формуле (9):

$$M = P_{вх} - i \cdot K_{сч}, \quad (9)$$

где  $M$  – состояние счетчика;

$P_{вх}$  – число поступивших импульсов;

$K_{сч}$  – коэффициент счета;

$i$  – количество полных циклов счета.

Счетчики могут классифицироваться по многим параметрам. Рассмотрим некоторые из них.

**По коэффициенту счета:** двоичные, модуль счета равен  $2^n$ , с произвольным коэффициентом счета,  $K_{сч} < 2^n$ .

**По направлению счета:** суммирующие, вычитающие и реверсивные.

По способу организации межразрядных связей:

- **с последовательным переносом**, в которых переключение триггеров разрядов осуществляется последовательно один за другим;

- **с параллельным переносом**, в которых переключение всех триггеров происходит одновременно по сигналу синхронизации;

- **с комбинированным переносом**, при котором используются различные комбинации способов переноса.

Классификационные признаки независимы и могут использоваться в различных сочетаниях, например, вычитающий счетчик с параллельным переносом.

**Счетчики могут использоваться как делители частоты.** На выходе такого устройства частота следования импульсов будет меньше частоты следования импульсов на входе в  $K_{\text{сч}}$  раз. В этом случае коэффициент счета определяется как коэффициент деления  $K_{\text{дел}}$ . В таком режиме работы у счетчика используется выходной сигнал только последнего триггера. В этом случае в схеме организуются дополнительные связи, и могут вводиться дополнительные логические элементы.

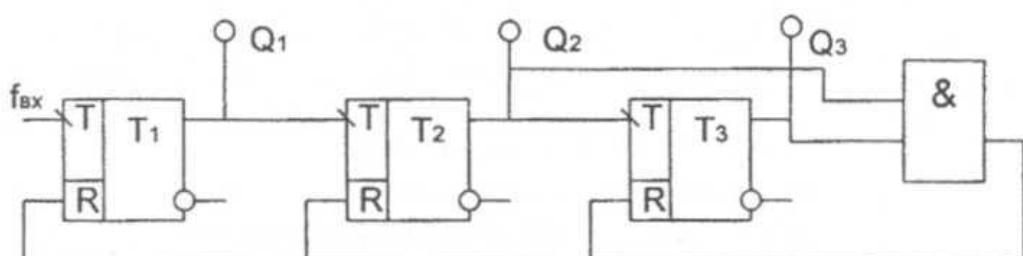

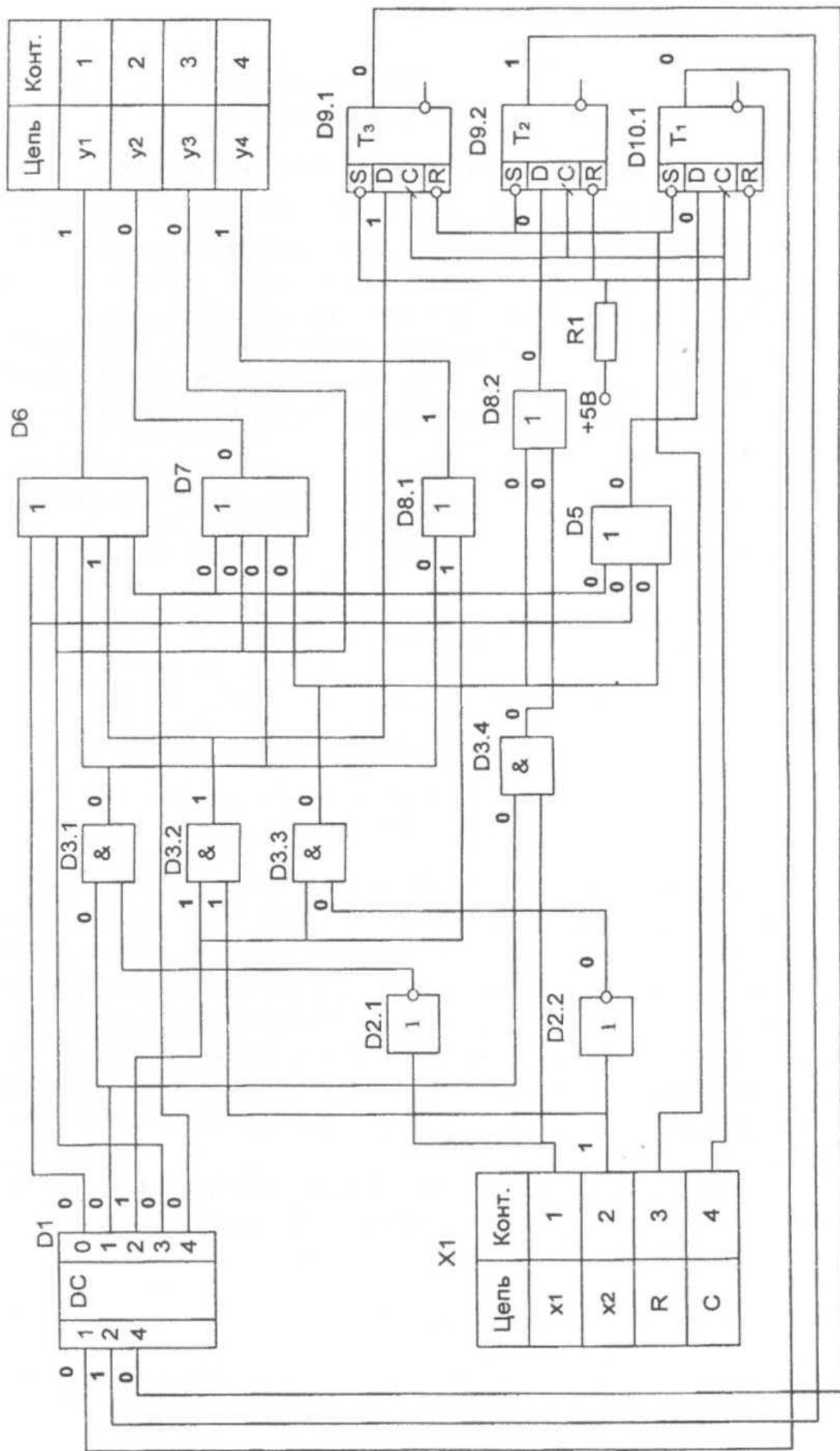

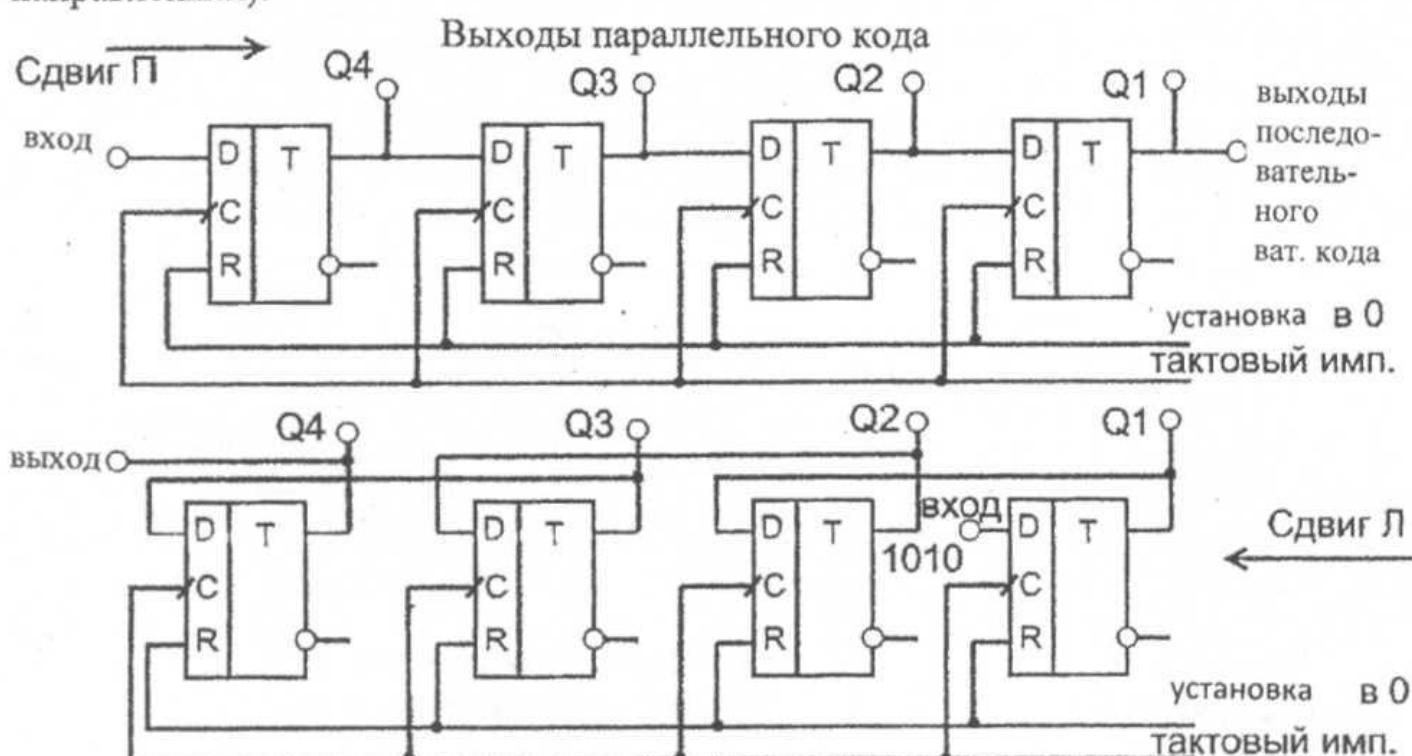

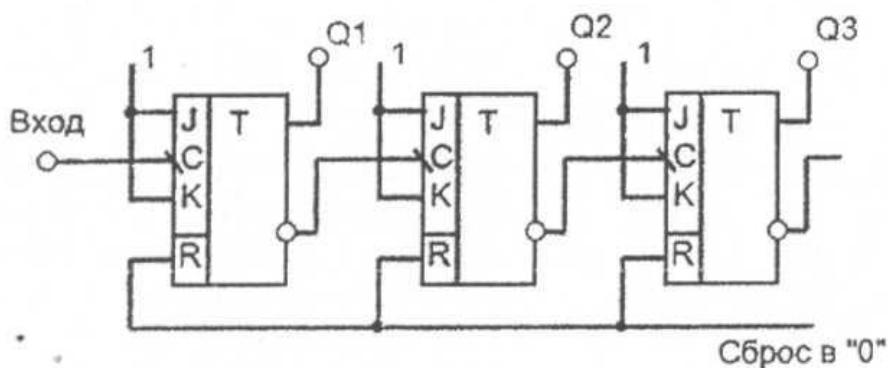

Рассмотрим пример построения делителя на шесть. За основу возьмем последовательный суммирующий счетчик (рис. 6). Запишем коэффициент деления двоичным кодом:  $K_{\text{дел}} = 6_{(10)} = 110_{(2)}$ . В записи коэффициента деления три разряда. Это значит, счетчик будет построен на трех триггерах, что позволит получить восемь состояний, а по условию требуется шесть. Для устранения избыточных состояний в схему вводится дополнительно логический элемент: если входы R триггеров прямые, то требуется взять элемент И, а если инверсные - то элемент И-НЕ. Количество входов этого элемента равно числу единиц в записи  $K_{\text{дел}}$  двоичным кодом. К входам элемента надо подключить прямые выходы триггеров, которым в этой записи соответствуют единицы, т.е. триггеры  $T_3$  и  $T_2$ .

Рис. 6. Делитель с  $K_{\text{дел}}=6$

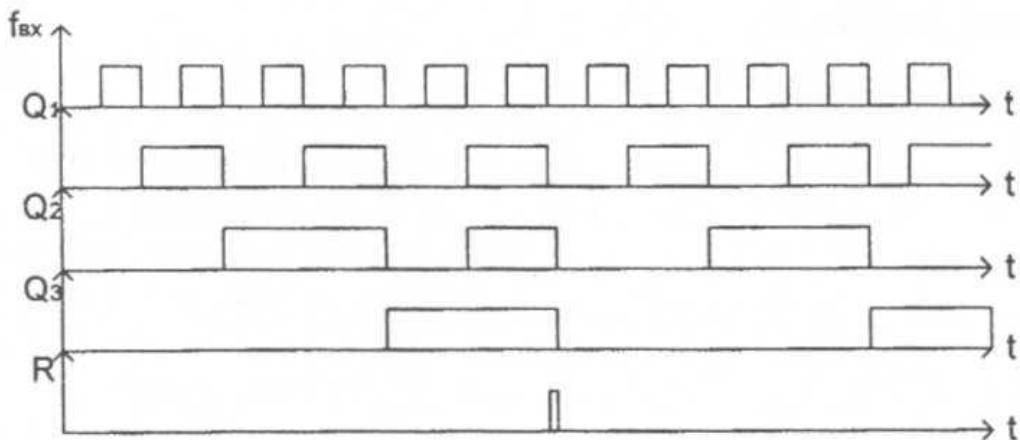

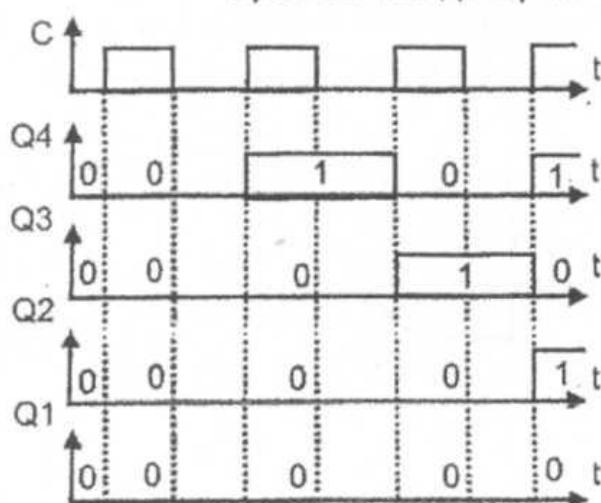

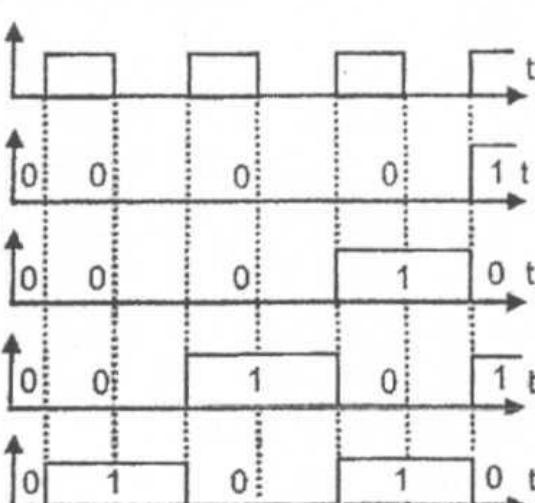

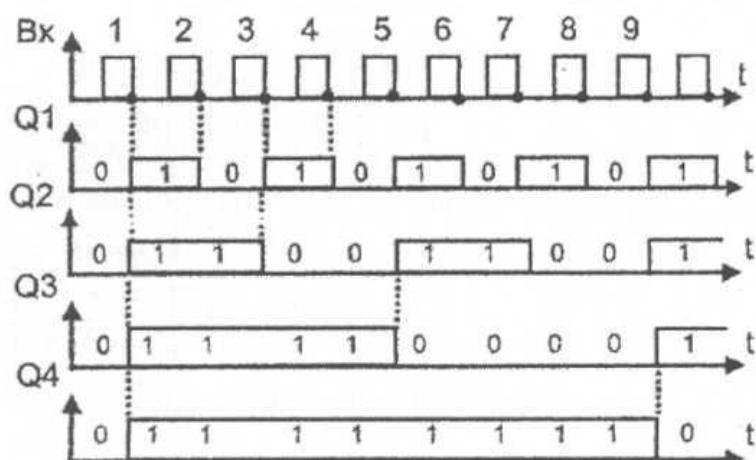

Временная диаграмма работы делителя приведена на рис. 7.

Рис. 7. Временная диаграмма работы делителя с  $K_{\text{дел}}=6$

Работа начинается при нулевом состоянии всех триггеров. Когда второй и третий триггеры перейдут в состояние “1”, что соответствует числу шесть, на выходе логического элемента И сформируется единица, которая поступает на все R –входы триггеров и они обнуляются. Счет начинается сначала.

По такому принципу можно строить и счетчики с произвольным коэффициентом счета. Однако в этом случае надо предусмотреть дополнительно вход начальной установки.

## **РАЗДЕЛ 4. УСТРОЙСТВА ЭВМ**

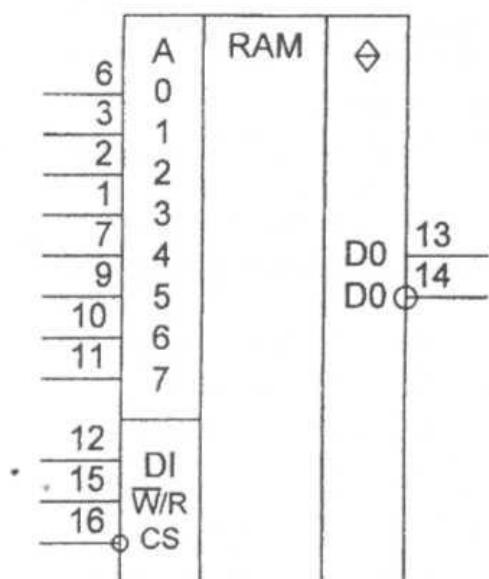

### **Тема 4.1. Запоминающие устройства ЭВМ**

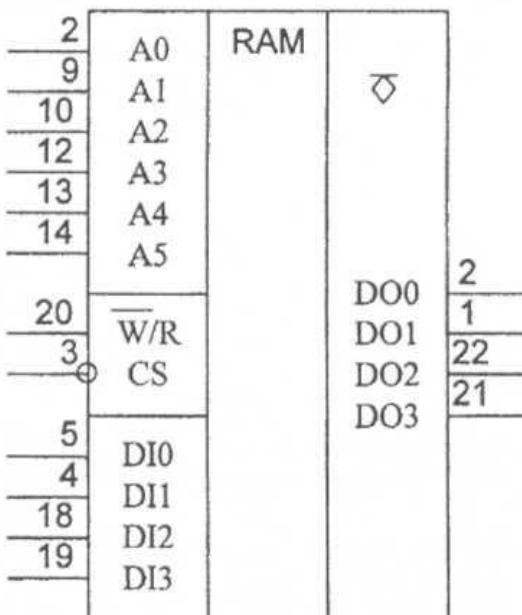

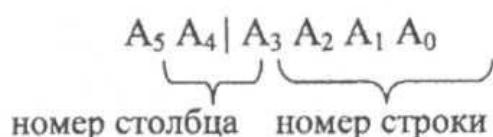

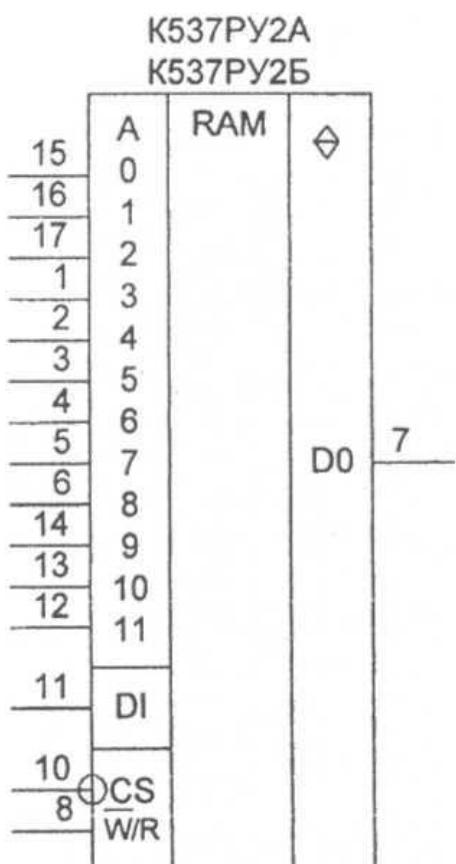

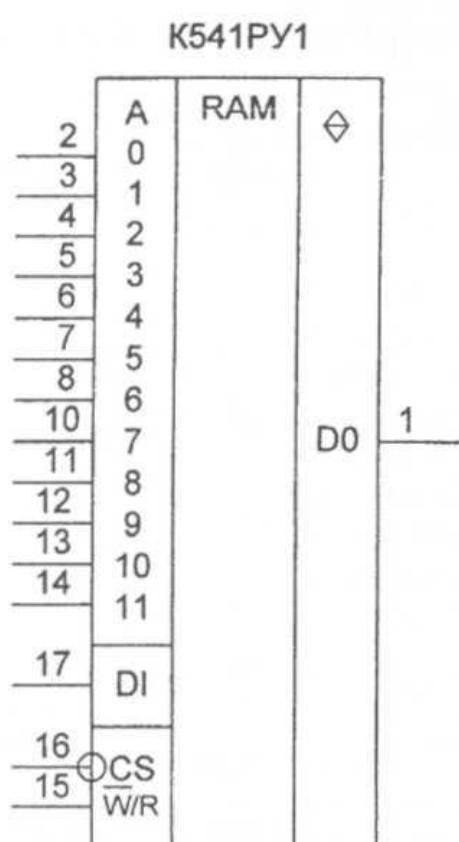

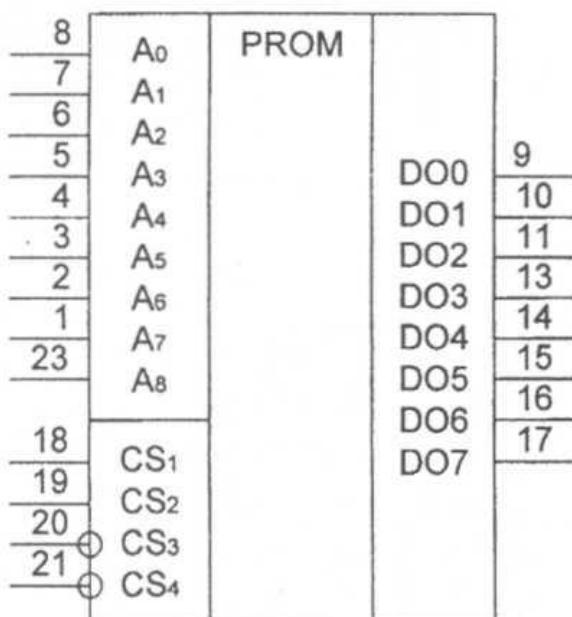

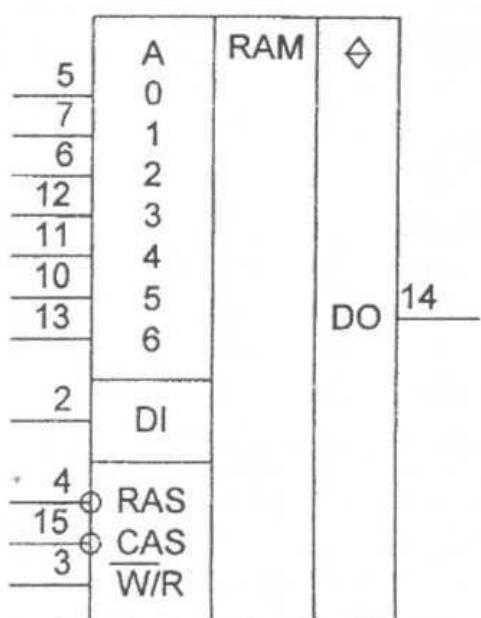

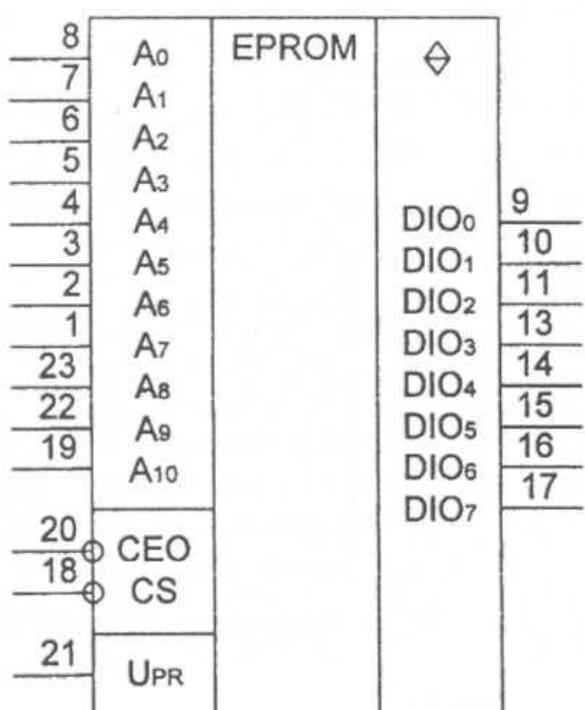

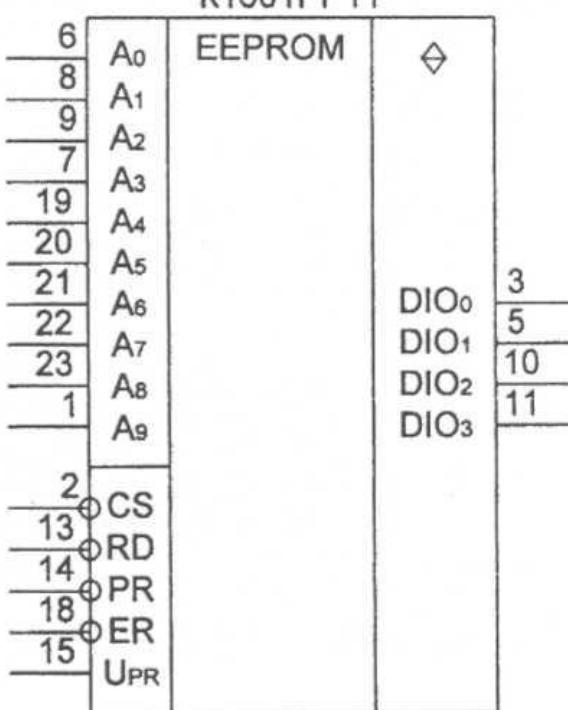

Классификация, параметры запоминающих устройств. ПЗУ, ОЗУ, кэш-память, буферное ЗУ. ВЗУ. Организация ЗУ: адресная, словарная, двухкоординатная, стековая, с произвольной выборкой, ассоциативная. Назначение, классификация ПЗУ: масочные, программируемые, репрограммируемые. УГО. Схемотехника постоянных запоминающих устройств (ПЗУ). Назначение ОЗУ. Статические и динамические микросхемы ОЗУ. Построение модулей памяти на базе интегральных микросхем. Кэш-память: принцип организации, назначение. Микросхемотехника оперативных запоминающих устройств. Внешние запоминающие устройства: принцип работы, конструкции. Основные характеристики.

### **Тема 4.2. Процессоры ЭВМ**

Процессор: состав, назначение. АЛУ: структура, типы, выполняемые операции. Устройства управления: схемно-логического и микропрограммного типов. Понятие о прерываниях, виды прерываний.

### **Тема 4.3. Интерфейсы в ВТ**

Состав, назначение, требования, типы. Параллельные и последовательные. Режимы работы симплексный, дуплексный и полудуплексный. Интерфейсы ЭВМ «общая шина» и «мультишина». Основные характеристики.

## **РАЗДЕЛ 5. МИКРОПРОЦЕССОРЫ (МП) И МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ (МПС)**

### **Тема 5.1. Архитектура МП**

Классификация. Структурная схема МП. Состав, назначение и взаимодействие отдельных блоков МП. Основные характеристики. CISC и RISC процессоры.

### **Тема 5.2. Архитектура МПС**

Особенности построения МПС. Понятие о вычислительных системах и их видах. Микропроцессорные комплексы: состав, назначение отдельных БИС. Ресурсы МПС: Система прерываний, система прямого доступа в память.

### **Тема 5.3. Применение СВТ в технике связи**

Процессоры, применяемые в ПК. Особенности однокристальных микро-ЭВМ. PIC-контроллеры и области их применения в связи.

## **МЕТОДИЧЕСКИЕ УКАЗАНИЯ по выполнению домашней контрольной работы**

### **Общие указания**

Каждое контрольное задание содержит пять задач. Перед решением каждой задачи изучите рекомендуемый материал и методические указания по соответствующим темам программы.

При оформлении работы необходимо придерживаться следующих требований:

1. Работа выполняется в ученической тетради. Количество страниц должно быть достаточным для размещения всех заданий с решением, для рецензии преподавателя и последующей работы над ошибками.

2. Вначале следует переписать условие задачи с данными своего варианта.

3. Ответы надо приводить сразу же после каждого пункта условия задачи.

4. Условные графические обозначения элементов и узлов приводить в соответствии с требованиями ГОСТ 2.743-91. Краткие сведения из этого стандарта приведены в приложении В.

5. Страницы, рисунки, таблицы должны быть пронумерованы. Рисунки и таблицы должны быть подписаны (ГОСТ 2. 105-95).

6. Ответы должны быть конкретными, краткими, четкими.

7. Работу над ошибками выполняйте не в тексте контрольной работы, а после рецензии преподавателя.

8. Если работа не зачтена, то ее следует выполнить вновь и отправить на проверку вместе с первой.

**Без представленной зачтенной контрольной работы, а так же при невыполнении лабораторных работ студенты к сдаче экзамена не допускаются.**

## КОНТРОЛЬНАЯ РАБОТА

### Задача № 1

Таблица 8

| Номер варианта | Логическая функция                                                                     | Набор аргументов для проверки |    |    |

|----------------|----------------------------------------------------------------------------------------|-------------------------------|----|----|

|                |                                                                                        | X1                            | X2 | X3 |

| 1              | $X_1 * X_2 * \bar{X}_3 \vee \bar{X}_1 * X_3 \vee X_1 * \bar{X}_3 \vee X_2$             | 1                             | 1  | 0  |

| 2              | $X_2 \vee X_1 * X_3 \vee X_2 * X_3 \vee \bar{X}_1 * X_2 * \bar{X}_3$                   | 1                             | 1  | 1  |

| 3              | $X_3 \vee X_1 * \bar{X}_2 \vee \bar{X}_2 * X_3 \vee \bar{X}_1 * X_2 * X_3$             | 0                             | 0  | 1  |

| 4              | $\bar{X}_2 \vee \bar{X}_1 * X_3 \vee X_1 * \bar{X}_3 \vee \bar{X}_1 * X_2 * \bar{X}_3$ | 0                             | 1  | 1  |

| 5              | $X_3 \vee \bar{X}_1 * \bar{X}_2 \vee X_1 * X_2 \vee \bar{X}_1 * X_2 * X_3$             | 0                             | 0  | 0  |

| 6              | $\bar{X}_1 \vee X_2 * X_3 \vee \bar{X}_2 * \bar{X}_3 \vee X_1 * \bar{X}_2 * X_3$       | 1                             | 0  | 1  |

| 7              | $X_1 \vee X_1 * \bar{X}_3 \vee X_2 * \bar{X}_3 \vee X_1 * \bar{X}_2 * X_3$             | 1                             | 0  | 0  |

| 8              | $X_1 \vee X_1 * \bar{X}_3 \vee \bar{X}_2 * X_3 \vee X_1 * \bar{X}_2 * \bar{X}_3$       | 0                             | 1  | 1  |

| 9              | $X_2 \vee \bar{X}_1 * \bar{X}_3 \vee X_1 * \bar{X}_3 \vee \bar{X}_1 * X_2 * X_3$       | 0                             | 0  | 1  |

| 10             | $X_1 \vee X_1 * \bar{X}_2 \vee \bar{X}_2 * X_3 \vee X_1 * X_2 * \bar{X}_3$             | 0                             | 1  | 0  |

Задана логическая функция  $f(x_1, x_2, x_3)$ , табл. 8.

- Постройте схему в базисе И, ИЛИ, НЕ.

- Постройте эту схему в базисе И, ИЛИ, НЕ на микросхемах серии K155 (KP1533).

- Выполните преобразование заданной логической функции так, чтобы она была представлена через операцию И-НЕ.

- Постройте логическую схему в базисе И-НЕ на микросхемах серии KP1533 (K155).

- На всех построенных схемах укажите логические сигналы на входах и выходах каждого элемента для кодовой комбинации, заданной табл. 9.

- Определите количество микросхем, используемых для построения схем в п.2 и п.4. Сделайте вывод о том, какой способ реализации более экономичен.

## Методические указания по выполнению задачи № 1

В ходе решения этой задачи предполагается, что студент, изучив предварительно соответствующий теоретический материал ([1, 2, с. 34 - 38, 51 - 59, 63 - 71]), приобретает навыки построения логических схем в базисах И, ИЛИ, НЕ и И-НЕ, а также в выполнении преобразований логических выражений с использование законов алгебры логики (правило де Моргана).

Порядок решения:

- выпишите из табл. 8 функцию, соответствующую вашему варианту;

- в результате анализа определите, какие логические элементы и в каком количестве потребуются для построения схемы.

При построении логической схемы следует учитывать приоритет выполнения операций:

- операция НЕ (инверсия);

- операция И (конъюнкция);

- операция ИЛИ (дизъюнкция).

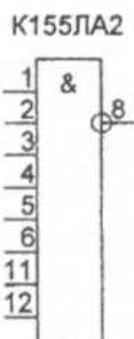

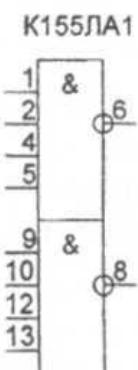

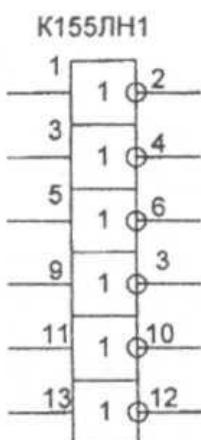

При построении логических схем с учетом конкретной серии необходимо иметь в виду, что в их состав входят микросхемы с определенным числом входов. Элементы И и ИЛИ обычно на два входа (2И, 2ИЛИ), элементы И-НЕ - на 2, 3, 4, 8 входов (соответственно: 2И-НЕ, 3И-НЕ, 4И-НЕ, 8И-НЕ), элементы ИЛИ-НЕ – на два входа (2ИЛИ-НЕ).

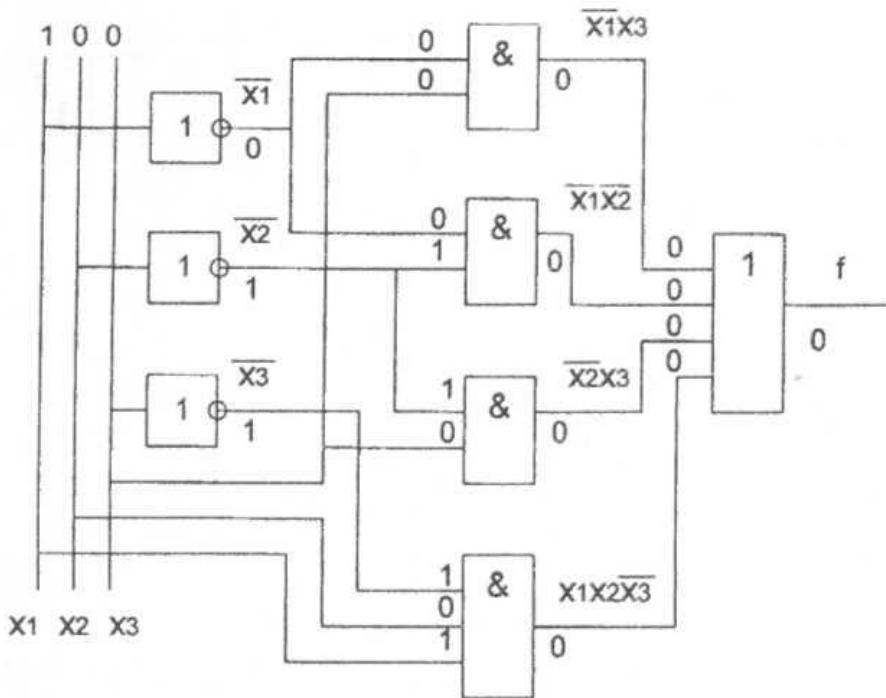

**Пример.** Задана логическая функция (10):

$$f = \overline{x_1}x_3 \vee \overline{x_1}x_2 \vee \overline{x_2}x_3 \vee x_1\overline{x_2}x_3 \quad (10)$$

Для построения схемы по приведенному выражению потребуется:

- три инвертора (все три аргумента входят в запись в инверсном и прямом значениях);

- три элемента 2И (для реализации выражений  $\overline{x_1}x_3$ ,  $\overline{x_1}x_2$ ,  $\overline{x_2}x_3$ );

- один элемент 3И (для реализации выражения  $x_1\overline{x_2}x_3$ );

- один элемент 4ИЛИ для объединения предварительных результатов преобразования на одну общую шину.

Схема имеет вид – рис. 8.

Рис. 8. Схема в базисе И, ИЛИ, НЕ

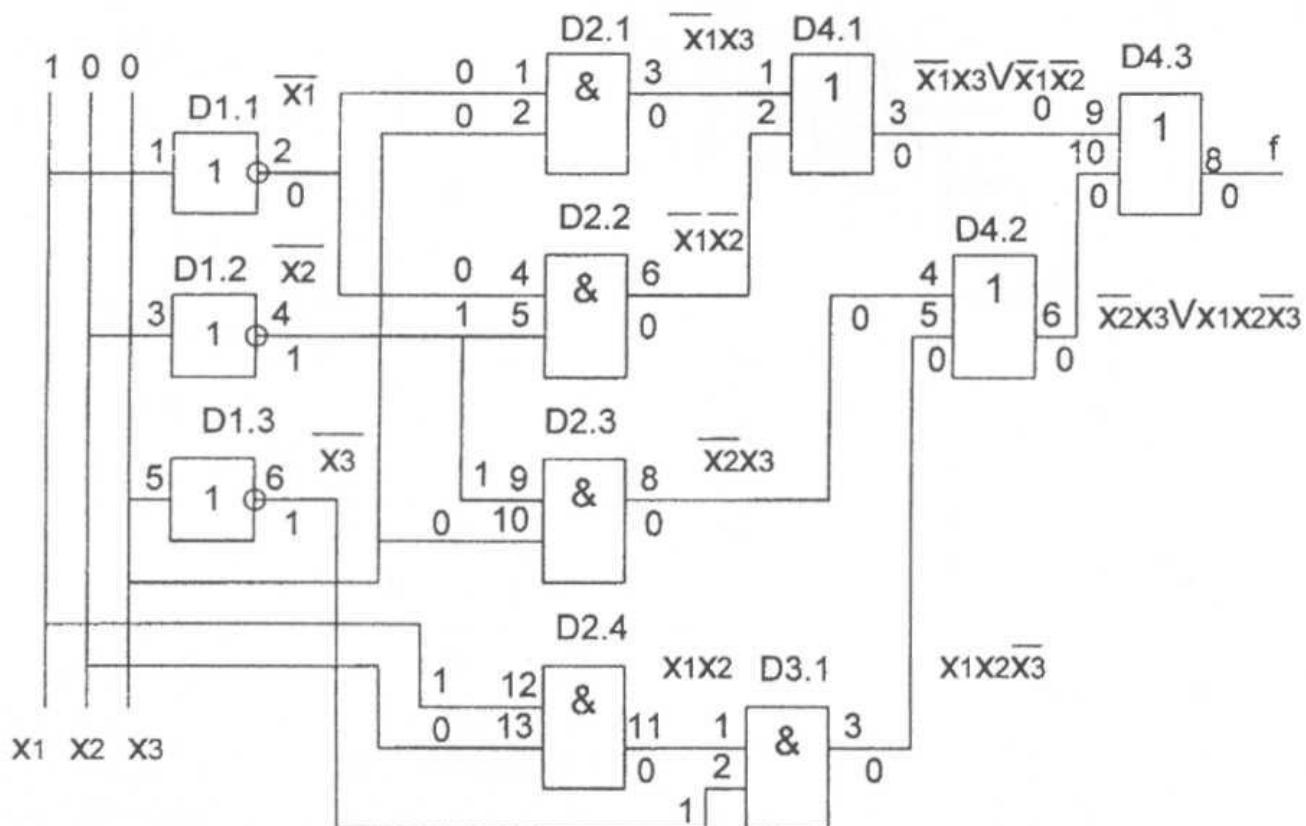

Следующую схему строим также в базисе И, ИЛИ, НЕ, но уже применительно к заданной серии микросхем. Перед этим необходимо внимательно изучить состав серии и правила применения микросхем по справочнику. В серии KP1533 есть микросхемы, которые содержат четыре элемента 2И-НЕ, (KP1533ЛН1), четыре логических элемента 2ИЛИ-НЕ (KP1533ЛЛ1), шесть логических элементов НЕ (KP1533ЛН1). С целью реализации схемы в базисе И, ИЛИ, НЕ на микросхемах серии K155 (KP1533) сделаем преобразование исходной функции (10).

$$f = \overline{x_1} \cdot \overline{x_3} \vee \overline{x_1} \cdot x_2 \vee x_2 \cdot \overline{x_3} \vee x_1 \cdot x_2 \cdot \overline{x_3} = (\overline{x_1} \cdot \overline{x_3}) \vee (\overline{x_1} \cdot x_2) \vee (x_2 \cdot \overline{x_3}) \vee ((x_1 \cdot x_2) \cdot \overline{x_3}) \quad (11)$$

Из этой записи следует, что для построения схемы потребуется три инвертора, пять элементов 2И, три элемента 2ИЛИ. Схема приведена на рис. 9.

В этой схеме использованы следующие микросхемы:

- D1 - KP1533ЛН1 (из шести элементов задействовано три);

- D2, D3, - KP1533ЛИ1 (один корпус используется полностью, а во втором только один);

- D4 – KP1533ЛЛ1 (один корпус, из четырех элементов используется три).

Рис. 9. Схема в базисе И, ИЛИ, НЕ на элементах серии KP1533

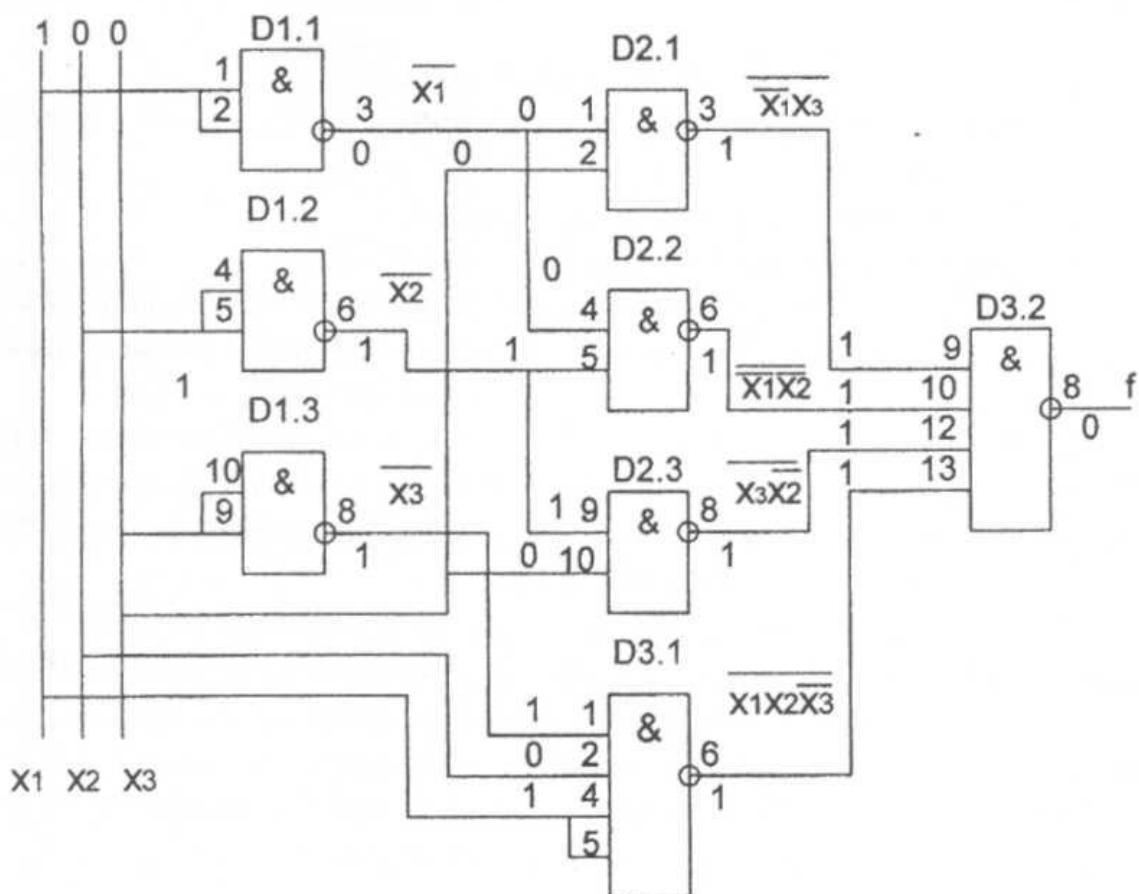

Для построения схемы в базисе И-НЕ необходимо выполнить преобразование исходного выражения так, чтобы оно было записано через операцию Штрих Шеффера. Для этого к исходному выражению применяем закон двойного отрицания и правило де Моргана.

$$\begin{aligned}

f &= \overline{x_1x_3} \vee \overline{x_1x_2} \vee \overline{x_2x_3} \vee x_1x_2\overline{x_3} = \overline{\overline{x_1x_3}} \vee \overline{\overline{x_1x_2}} \vee \overline{\overline{x_2x_3}} \vee \overline{x_1x_2}\overline{x_3} = \\

&= (\overline{x_1x_3})(\overline{x_1x_2})(\overline{x_2x_3})(\overline{x_1x_2}\overline{x_3})

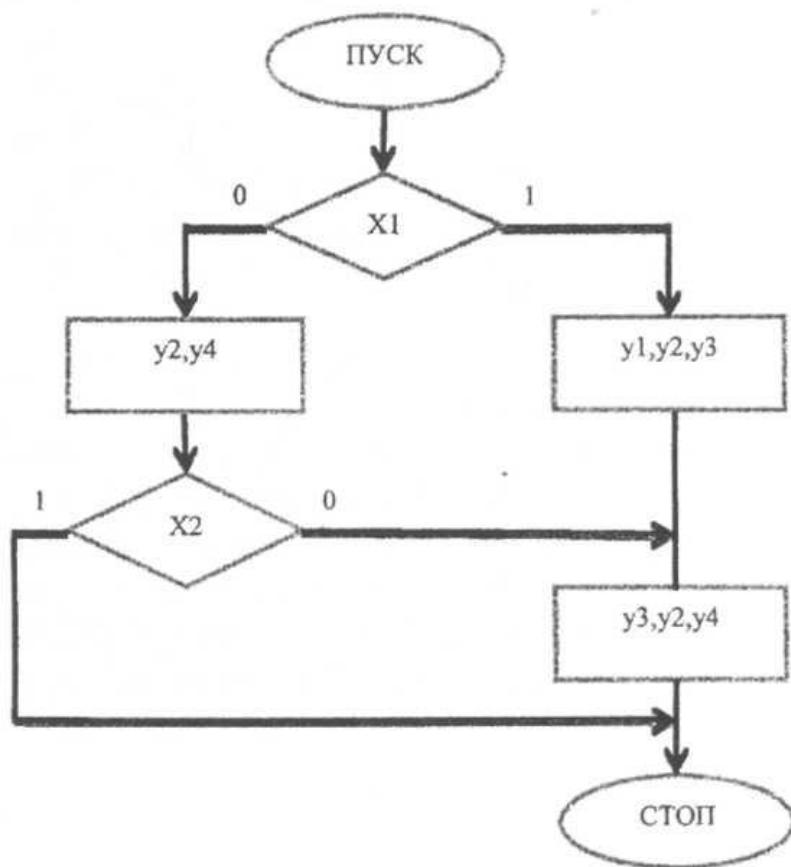

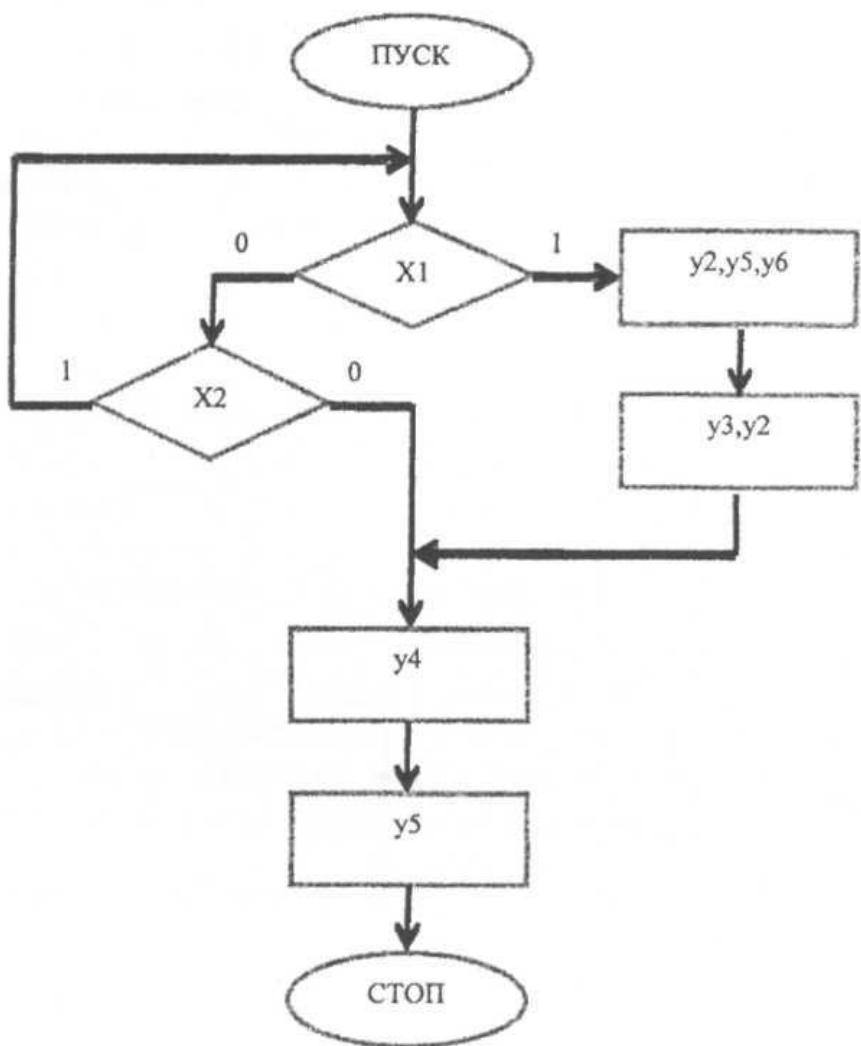

\end{aligned} \tag{12}$$