**ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ

УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ**

**«МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ

УНИВЕРСИТЕТ ПУТЕЙ СООБЩЕНИЯ»**

**Институт управления и информационных технологий**

**Кафедра «Вычислительные системы и сети»**

**А. Е. МАМЧЕНКО, М. И. ШАМРОВ**

**ОРГАНИЗАЦИЯ, СХЕМОТЕХНИКА

И МИКРОПРОГРАММИРОВАНИЕ

ПРОЦЕССОРОВ ЭВМ**

Рекомендовано редакционно-издательским советом университета

в качестве методических указаний для студентов, обучающихся

по направлению «Информатика и вычислительная техника»

**МОСКВА - 2012**

**УДК 681.3

М-22**

Мамченко А. Е., Шамров М. И. Организация, схемотехника и микропрограммирование процессоров ЭВМ. Методические указания к курсовому проектированию по дисциплине «Организация ЭВМ и систем». -М.: МИИТ, 2012, - 66с.

В методических указаниях приведены основные сведения о проектируемых процессорах, задания на их проектирование, описание элементной базы, общие рекомендации по выполнению и требования по оформлению курсовых проектов

© МИИТ, 2012

## **Введение**

Курсовой проект по дисциплине «Организация ЭВМ и систем» является важным и одним из сложных учебных заданий, выполняемых студентами в рамках профессиональной подготовки по направлению «Информатика и вычислительная техника». В нем разрабатывается программируемое управляемое устройство на базе больших интегральных схем (БИС) многокристальных микропроцессоров, решаются нетривиальные и трудно формализуемые вопросы реального проектирования устройств вычислительной техники:

- выбор архитектуры,

- разработка общей структурной организации,

- разработка аппаратных и микропрограммных средств.

Оформление конструкторских документов проекта требует освоения системы автоматизированного проектирования цифровых устройств.

Указания содержат задания и рекомендации по их реализации для двух тем курсового проекта:

1. Программируемый логический контроллер на многокристальном микропроцессоре (раздел 1);

2. Сопроцессор с архитектурой RISC (раздел 2).

В разделах 3, 4 приведено краткое описание используемой в проекте элементной базы и даны варианты ее применения в проектируемых устройствах.

Раздел 5 определяет общие требования к оформлению курсового проекта решения и содержанию пояснительной записки. Перечень литературы приведен в разделе 6.

# 1. Программируемый логический контроллер на многокристальном микропроцессоре

## **1.1. Общие сведения о проектируемом устройстве.**

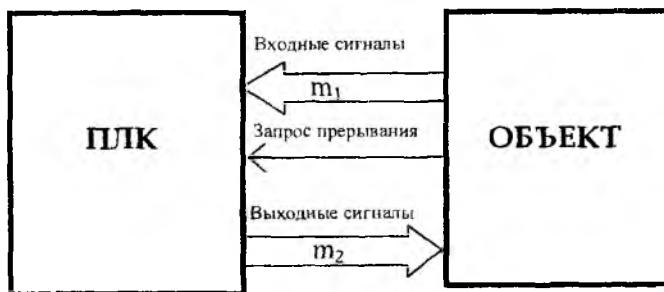

Программируемый логический контроллер (далее ПЛК) представляет собой простейшую специализированную ЭВМ для управления несложными объектами и технологическими процессами [1]. Входными сигналами ПЛК служат сигналы от  $m_1$  двоичных датчиков объекта и, возможно, сигналы прерываний. Выходные сигналы передаются контроллером к  $m_2$  исполнительным механизмам (рис.1).

Рис. 1.1. Связи ПЛК с объектом управления

Система команд ПЛК ориентирована на выполнение следующих функций:

- вычисление любой (с учетом ограничений на объем программной памяти) из  $m_2$  булевых функций от  $m_1$  аргументов

$Y_j = f_j(x_0, x_1, \dots, x_b, \dots, x_{m_1-1})$ , где  $j = 0, 1, \dots, m_2 - 1$ ;

- реализация простейших вычислительных процедур, используемых, в основном, для реализации временных задержек;

- обработка запроса прерывания.

Управление объектом осуществляется по программам, фиксируемым пользователем в постоянной памяти программ (ПП). Для хранения промежуточных данных и состояний прерываемых программ используется память данных (ПД).

## **1.2. Задание на проектирование ПЛК**

Вариантом задания является строка из таблицы 1.1, номер которой совпадает с номером студента в журнале студенческой группы.

В строке указаны параметры устройств, входящих в состав ПЛК. Первые четыре параметра в строке определяют параметры памяти и блоков ввода-вывода:

$C_{пп}$  - количество ячеек памяти программ ПП (емкость ПП),

$C_{пд}$  - количество ячеек памяти данных ПД (емкость ПД),

$m_1$  - количество портов ввода для приема входных сигналов,

$m_2$  - количество портов вывода для выдачи выходных сигналов.

Параметр «ТИП АРХИТЕКТУРЫ И АДРЕСАЦИЯ ПДЭ» определяет организацию адресных пространств всех программно доступных элементов (ПДЭ) памяти и портов ввода-вывода:

1 - адресные пространства ПП и ПД организуются по принципу гарвардской архитектуры, а порты ввода и порты вывода адресуются в собственных адресных пространствах;

2 - адресные пространства ПП и ПД организуются по принципу принстонской архитектуры и образуют общее адресное пространство с портами ввода и вывода.

Параметр « НАЛИЧИЕ ПЕРЕКЛЮЧАТЕЛЯ S» задает наличие или отсутствие переключателя S, устанавливающего режим работы ПЛК:

«ОСТАНОВ» - режим ожидания,

«РАБОТА» - режим исполнения программ.

Таблица 1.1.

Варианты заданий

| №<br>п/з | Емкость памяти<br>программ (ячеек)<br>Спр | Емкость памяти<br>данных (ячеек)<br>Сдд | Число<br>портов      |                       | Тип архитектуры<br>адресации ПДС | Панель<br>переключателя<br>S | Запрос<br>прерывания |                    | Элементная ба-<br>за процессора |

|----------|-------------------------------------------|-----------------------------------------|----------------------|-----------------------|----------------------------------|------------------------------|----------------------|--------------------|---------------------------------|

|          |                                           |                                         | ввода m <sub>1</sub> | вывода m <sub>2</sub> |                                  |                              | маскиру-<br>мый      | немаски-<br>руемый |                                 |

| 1        | 256                                       | 256                                     | 32                   | 4                     | 1                                | да                           | +                    |                    | K1804                           |

| 2        | 512                                       | 256                                     | 8                    | 8                     | 2                                | нет                          |                      | +                  | K589                            |

| 3        | 256                                       | 512                                     | 16                   | 4                     | 2                                | да                           | +                    |                    | K589                            |

| 4        | 2048                                      | 256                                     | 8                    | 4                     | 2                                | нет                          |                      | +                  | K1804                           |

| 5        | 1024                                      | 512                                     | 4                    | 8                     | 1                                | да                           | +                    |                    | K589                            |

| 6        | 1024                                      | 64                                      | 8                    | 4                     | 1                                | нет                          |                      | +                  | K589                            |

| 7        | 256                                       | 128                                     | 16                   | 16                    | 1                                | да                           | +                    |                    | K1804                           |

| 8        | 256                                       | 64                                      | 16                   | 16                    | 2                                | да                           |                      | +                  | K589                            |

| 9        | 1024                                      | 512                                     | 8                    | 8                     | 1                                | нет                          | +                    |                    | K589                            |

| 10       | 512                                       | 2048                                    | 4                    | 4                     | 2                                | да                           |                      | +                  | K1804                           |

| 11       | 2048                                      | 256                                     | 4                    | 8                     | 2                                | да                           | +                    |                    | K1804                           |

| 12       | 512                                       | 64                                      | 4                    | 12                    | 2                                | нет                          |                      | +                  | K589                            |

| 13       | 256                                       | 256                                     | 32                   | 16                    | 1                                | нет                          | +                    |                    | K1804                           |

| 14       | 512                                       | 256                                     | 8                    | 4                     | 2                                | нет                          |                      | +                  | K589                            |

| 15       | 2048                                      | 64                                      | 4                    | 12                    | 2                                | да                           | +                    |                    | K1804                           |

| 16       | 2048                                      | 128                                     | 12                   | 4                     | 2                                | да                           |                      | +                  | K1804                           |

| 17       | 1024                                      | 256                                     | 8                    | 8                     | 1                                | да                           | +                    |                    | K589                            |

| 18       | 4096                                      | 1024                                    | 4                    | 8                     | 1                                | нет                          |                      | +                  | K1804                           |

| 19       | 2048                                      | 512                                     | 8                    | 4                     | 2                                | да                           | +                    |                    | K1804                           |

| 20       | 1024                                      | 512                                     | 16                   | 8                     | 1                                | да                           |                      | +                  | K589                            |

| 21       | 512                                       | 256                                     | 8                    | 8                     | 2                                | да                           | +                    |                    | K589                            |

| 22       | 2048                                      | 256                                     | 12                   | 4                     | 2                                | нет                          |                      | +                  | K1804                           |

| 23       | 256                                       | 64                                      | 8                    | 4                     | 1                                | да                           | +                    |                    | K1804                           |

| 24       | 4096                                      | 1024                                    | 4                    | 8                     | 1                                | нет                          |                      | +                  | K1804                           |

Параметр «ЗАПРОС ПРЕРЫВАНИЯ» определяет наличие или отсутствие маскирования прерывания, формируемого объектом управления.

Параметр «ЭЛЕМЕНТНАЯ БАЗА ПРОЦЕССОРА» определяет серию интегральных схем, используемую для построения процессора ПЛК. Описание серий можно найти в разделе 3 настоящих указаний и в справочной литературе, перечисленной в разделе 6.

### **1.3. Рекомендации по разработке ПЛК.**

#### **Архитектура ПЛК**

Под архитектурой ПЛК, как и любой ЭВМ, чаще всего понимают набор сведений, необходимый программисту-пользователю для написания программ на языке машинных команд. Кроме структуры в архитектуру ПЛК включают:

- типы, формы представления и форматы обрабатываемых данных;

- программистскую модель;

- сведения о системе команд и используемых способах адресации;

- сведения об организации систем прерывания и ввода-вывода информации.

Разработка архитектуры ПЛК предшествует этапам системотехнического, схемотехнического и конструкторского проектирования, причем ПЛК с одной и той же архитектурой могут быть реализованы с использованием различных инженерных решений.

#### **Структурно-логическая организация и функционирование ПЛК**

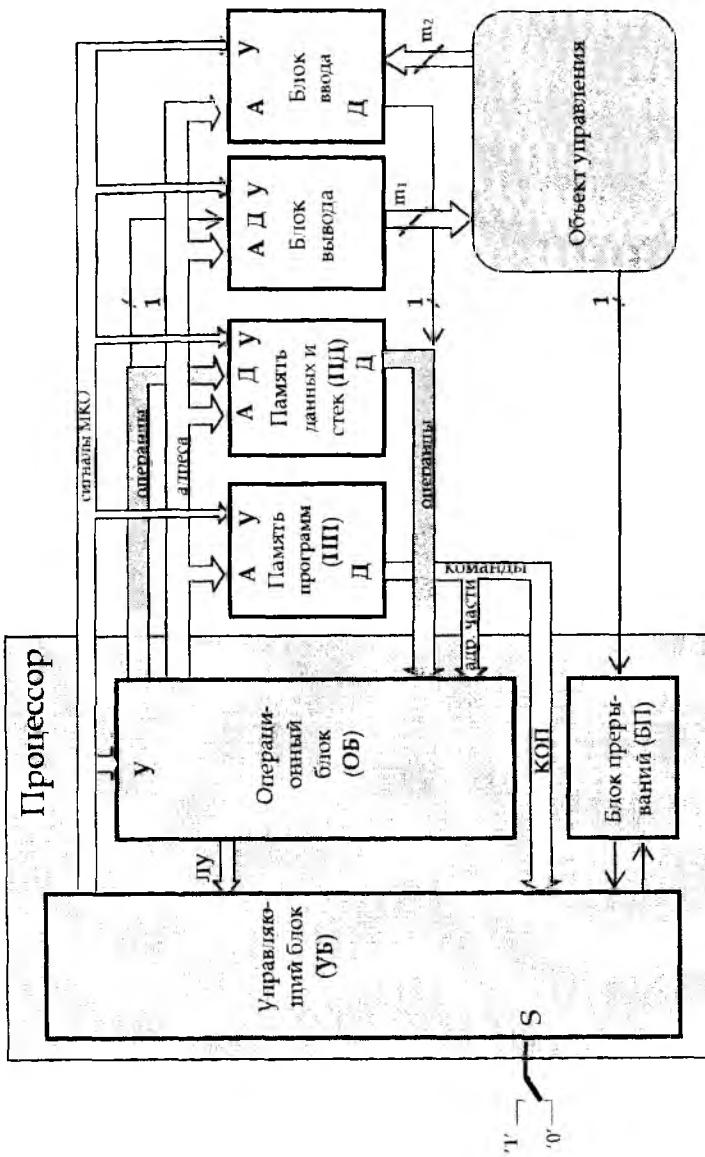

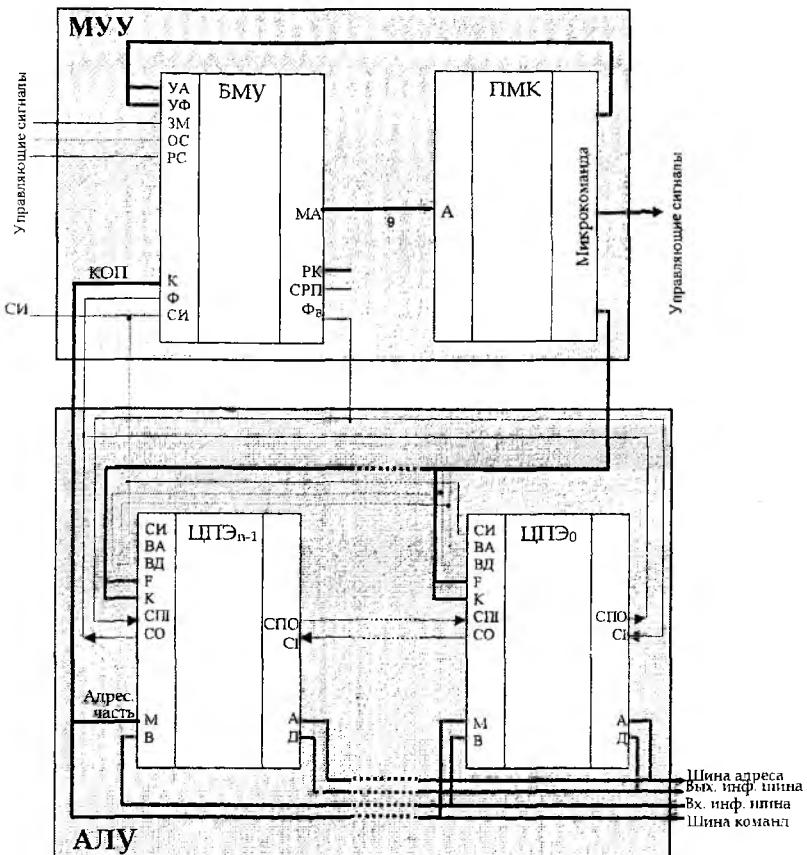

Укрупненная структурная схема ПЛК показана на рис.1.2. Основу ПЛК составляет процессор, состоящий из двух блоков: операционного (ОБ) и управляющего (УБ),

Рис. 1.2. Укрупненная структурная схема ПЛК

что соответствует принципу декомпозиции цифрового устройства на операционную и управляющую части. Кроме этого в состав процессора входит блок прерываний (БП). Процессор подключен посредством адресных (A), информационных (Д) и управляющих (У) шин к памяти программ (ПП), памяти данных (ПД) и блокам ввода-вывода (БВВ). При проектировании ПЛК данная схема уточняется и детализируется в соответствии с заданием.

Адресное взаимодействие процессора с устройствами ПП, ПД, БВВ осуществляется путем формирования в операционном блоке адресов обращения и их передачи в эти устройства с добавлением необходимых управляющих сигналов (выбор устройств, режим обращения и т.п.). Запись операндов может быть осуществлена из ОБ в память данных ПД или в блок вывода. Адресные части команд из ПП и операнды из ПД и блока ввода принимаются в ОБ, а коды операций команд (КОП) принимаются в управляющий блок УБ для последующей дешифрации.

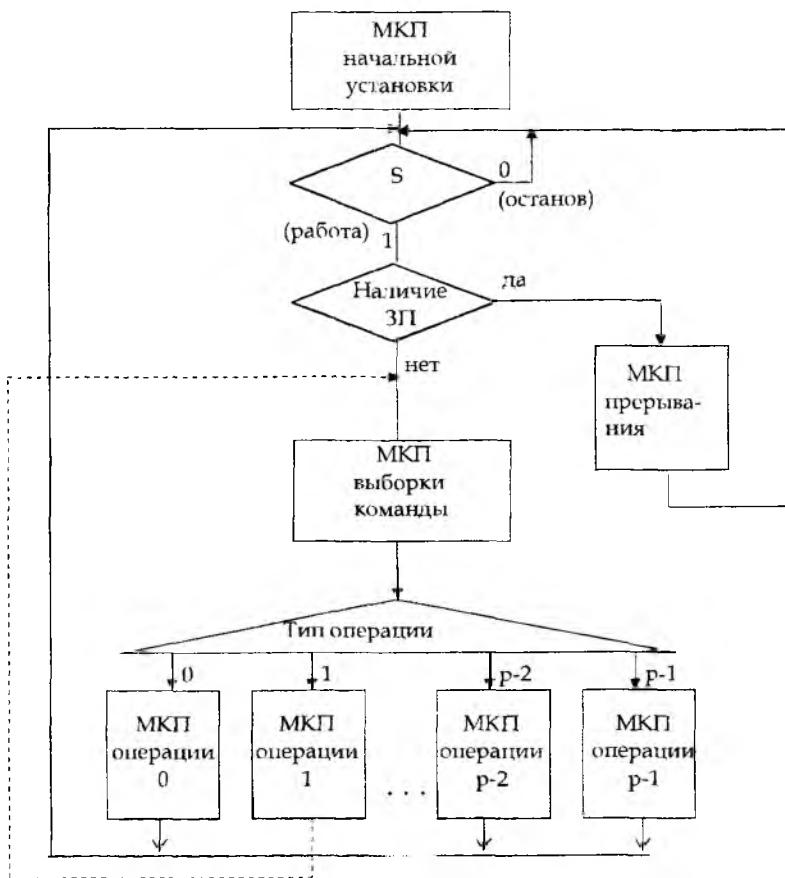

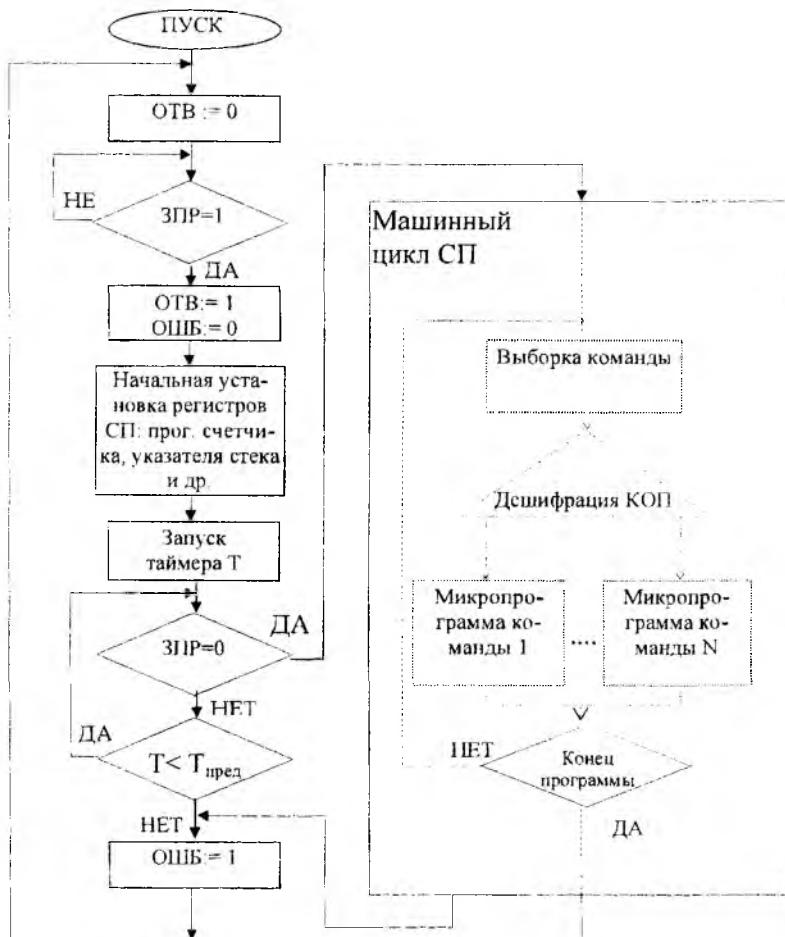

Управляющий блок строится в проекте как автомат с программируемой (хранимой в памяти) логикой. Осведомительными сигналами или сигналами логических условий (ЛУ) для него являются флаги (признаки), вырабатываемые блоком ОБ, сигналы от БП и сигнал от переключателя S. При этом нулевому значению S соответствует режим “останов”, а единичному – “работа”. Укрупненная блок-схема микропрограммы, реализующей рабочий цикл процессора ПЛК, представлена на рис. 1.3.

Сложность реальной микропрограммы рабочего цикла ПЛК зависит от числа и сложности команд, организации их выборки и обработки, набора микроопераций в ОБ, типа запроса прерываний, наличия переключателя S.

Микропрограмма (МКП) начальной установки (адрес ее начала должен устанавливаться в УБ автоматически после включения ПЛК или по нажатию специальной кнопки) осуществляет обычно следующие действия:

Рис.1.3. Укрупненная блок-схема микропрограммы рабочего цикла ПЛК

- обнуление программного счетчика (PC) в ОБ, что обеспечивает выборку первой команды из 0-ой ячейки ПП;

- установка в начальное состояние триггеров БП, триггеров фиксации выходных сигналов в блоке вывода и т.п.

Анализ состояния переключателя S для перехода в режим “останов” или “работа” исключается при его отсутствии. Наличие прерывания проверяется путем опроса состояния сигнала запроса прерывания. При наличии запроса осуществляется переход к микропрограмме прерывания (см. ниже).

МКП выборки команды реализует обращение в ПП по адресу из программного счетчика с его последующей инкрементацией для перехода к следующей команде. КОП считанной из ПП команды подается в УБ для формирования адреса перехода к МКП выполнения операции, заданной командой.

### **Программистская модель, способы адресации и система команд ПЛК.**

Все компоненты архитектуры проектируемого ПЛК являются взаимосвязанными и должны соответствовать перечню операций и форматам команд, входящих в реализуемую систему команд.

Данными, обрабатываемыми в ПЛК, являются:

- a) k-разрядные целые числа без знака, представляющие собой адреса;

- б) n-разрядные числа без знака;

- в) булевы переменные в виде бита в n-разрядном двоичном коде (возможно в виде n-разрядных кодов с одинаковыми значениями разрядов).

Программистскую модель ПЛК составляют все программно-доступные, т.е. идентифицируемые командами (кодами операций и адресными частями команд) элементы, в которых располагаются сами команды, входные, выходные и промежуточные данные. Функционирование ПЛК

можно организовать с использованием программистской модели, включающей:

- программный счетчик РС;

- аккумулятор А;

- один регистр общего назначения - R<sub>i</sub>;

- С<sub>пп</sub> ячеек памяти программ;

- С<sub>пд</sub> ячеек памяти данных;

- m<sub>1</sub> однобитовых портов ввода, через которые в ПЛК поступают сигналы от m<sub>1</sub> датчиков объектов;

- m<sub>2</sub> однобитовых портов вывода, с которыми соединяются входы m<sub>2</sub> исполнительных механизмов;

- триггер разрешения/запрещения маскируемых прерываний, управляемый командами типа EI и DI;

Что касается регистра флагов, по битам которого организуются переходы в программах процессоров ЭВМ, то без него можно обойтись, если осуществлять переход только по нулевому содержимому аккумулятора А.

В командах ПЛК достаточно использовать подразумеваемую, непосредственную и прямую адресацию данных и програмно-доступных элементов. При выборе системы команд следует стремиться к минимальному их числу, удовлетворяя, однако, требованию алгоритмической полноты системы команд, т. е. возможности представления в терминах команд алгоритмов управления объектом и обслуживания прерываний.

С учётом этого требования и выбранных способов адресации достаточной оказывается система из шестнадцати команд и для кодирования кода операции используется четыре разряда, т.е. n<sub>код</sub>=4. Адресная часть команд с прямой адресацией определяется следующими формулами (с округлением до большего целого):

- в случае 1 (гарвардская архитектура):

$k = \log_2\{\max [C_{пп}, C_{пд}, m_1, m_2]\};$

- в случае 2 (принстонская архитектура):  $k = \log_2\{C_{\text{пр}} + C_{\text{пд}} + \max[m_1, m_2]\}$ .

Для приведенных в таблице 1.1 значений  $C_{\text{пр}}$ ,  $C_{\text{пд}}$ ,  $m_1$  и  $m_2$  значение  $k = 8; 10; 12$ .

Разрядность коротких команд, таких как EI, DI, IRET и др. определяется только кодом операции.

Выбор разрядности ячеек памяти программ ( $n_{\text{пр}}$ ), памяти данных ( $n_{\text{пд}}$ ) и операционного блока ( $n_{\text{об}}$ ) зависит, прежде всего, от того располагаются ли длинные и короткие команды в ячейках ПП одного (длинного) формата или для хранения длинных команд используются несколько ячеек ПП.

Более понятной и более быстродействующей будет организация ПЛК, в которой принято:

$$n_{\text{пр}} = n_{\text{код}} + k = 4+k;$$

$$n_{\text{пд}} = n = k;$$

$n_{\text{об}} = n$ , т.е. и короткие и длинные команды располагаются в ячейках памяти программ одной и той же разрядности, а разрядность ячеек памяти данных и ширина обработки в ОБ одинакова и равна  $n$ .

Для выбора системы команд и их форматов можно воспользоваться примером, приведенным в таблице 1.2. Здесь A - аккумулятор, R- регистр общего назначения, PC-программный счётчик , addr - адреса ПП или ПД, port – адреса портов ввода-вывода, data- непосредственный операнд, “~” - произвольное значение бита. Пример приведён для случая принстонской архитектуры с адресацией внешних ПДЭ в общем адресном пространстве и  $C_{\text{пр}}=128$ ,  $C_{\text{пд}}=64$  и  $m_1=m_2=16$ . Для их адресации используется  $2^k = 2^8 = 256$  адресов, причём адреса от 0 до 127 (от 00h до 7Fh) адресуют ячейки памяти программ (в командах JMP addr и JA addr разряд  $A_7 = 0$ ). Для адресации ячеек памяти данных выбираются следующие 64 адреса от 128 до 191 (от 80h до 0BFh) и в командах обращения к ПД  $A_7 = 1$  и  $A_6 = 0$ .

Таблица 1.2

## Пример системы команд

| Груп<br>лы<br>ко-<br>манд                                          | №<br>п/п | Мнемоника   | Операция                          | Формат команды |    |   |   |                |   |   |   |   |   |   |   | Время<br>выпол-<br>нения<br>(так-<br>тов/мк<br>с) |  |  |

|--------------------------------------------------------------------|----------|-------------|-----------------------------------|----------------|----|---|---|----------------|---|---|---|---|---|---|---|---------------------------------------------------|--|--|

|                                                                    |          |             |                                   | КОП            |    |   |   | Адресная часть |   |   |   |   |   |   |   |                                                   |  |  |

|                                                                    |          |             |                                   | 11             | 10 | 9 | 8 | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |                                                   |  |  |

| Команды пересылок и об-<br>ращения к ПД и блокам<br>ввода - вывода | 1        | MOV A, data | A←data                            | 0              | 0  | 0 | 0 |                |   |   |   |   |   |   |   |                                                   |  |  |

|                                                                    | 2        | MOV R, data | R←data                            | 0              | 0  | 0 | 1 |                |   |   |   |   |   |   |   |                                                   |  |  |

|                                                                    | 3        | MOV R, A    | R←A                               | 0              | 0  | 1 | 0 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 4        | MOVA, R     | A←R                               | 0              | 0  | 1 | 1 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 5        | MOV A, M    | A←(addr)                          | 0              | 1  | 0 | 0 | 1              | 0 |   |   |   |   |   |   | адрес ПД                                          |  |  |

|                                                                    |          |             | A←(port)                          | 0              | 1  | 0 | 0 | 1              | 1 | ~ | ~ |   |   |   |   | адрес порта<br>ввода                              |  |  |

|                                                                    | 6        | MOV M, A    | (addr)← A                         | 0              | 1  | 0 | 1 | 1              | 0 |   |   |   |   |   |   | адрес ПД                                          |  |  |

|                                                                    |          |             | (port)← A                         | 0              | 1  | 0 | 1 | 1              | 1 | ~ | ~ |   |   |   |   | адрес порта<br>вывода                             |  |  |

| Логические<br>операции                                             | 7        | NOT A       | A← $\bar{A}$                      | 0              | 1  | 1 | 0 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 8        | AND A, R    | A← A&R                            | 0              | 1  | 1 | 1 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 9        | OR A, R     | A← AvR                            | 1              | 0  | 0 | 0 |                |   |   |   |   |   |   |   | -                                                 |  |  |

| Арифмети-<br>ческие<br>операции                                    | 10       | DEC A       | A←A-1                             | 1              | 0  | 0 | 1 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 11       | DEC R       | R←R-1                             | 1              | 0  | 1 | 0 |                |   |   |   |   |   |   |   | -                                                 |  |  |

| Команды<br>переходов                                               | 12       | JMP addr    | PC← addr                          | 1              | 0  | 1 | 1 | 0              |   |   |   |   |   |   |   | адрес памяти программ                             |  |  |

|                                                                    | 13       | JA addr     | PC← addr<br>при A=0               | 1              | 1  | 0 | 0 | 0              |   |   |   |   |   |   |   | адрес памяти программ                             |  |  |

| Команды управ-<br>ления прерыва-<br>ниями                          | 14       | EI          | Разрешить<br>прерывание<br>TMI:=1 | 1              | 1  | 0 | 1 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 15       | DI          | Запретить<br>прерывание<br>TMI:=0 | 1              | 1  | 1 | 0 |                |   |   |   |   |   |   |   | -                                                 |  |  |

|                                                                    | 16       | IRET        | Возврат из<br>прерывания          | 1              | 1  | 1 | 1 |                |   |   |   |   |   |   |   | -                                                 |  |  |

Для обращения к портам используются команды с теми же кодами операциями, но адресами от 0C0h до 0FFh

$(A_7 = A_6 = 1)$ . При этом каждый из 16 портов – как ввода, так и вывода – адресуется четырьмя младшими разрядами адреса, а разряды  $A_5$ ,  $A_4$  – любые (неполная адресация, см. [2]).

В случае адресации портов в собственных адресных пространствах в системе команд имеют место команды IN port и OUT port со своими кодами операции.

Из анализа примера также следует, что запрос прерывания – маскируемый (команды 14 и 15).

В таблицу 1.2 следует также поместить времена выполнения команд – в тактах и микросекундах, которые определяются после микропрограммирования в реальных форматах микрокоманд и выбора периода импульса синхронизации (такта).

Для проверки алгоритмической полноты выбранной системы команд студенту нужно составить программу вычисления пары булевых функций от трёх-четырёх переменных и передачи их значений к исполнительным механизмам объекта через неравные промежутки времени.

## **Разработка функциональной схемы ПЛК, формата микрокоманды и микропрограмм.**

Функциональная схема ПЛК образуется из функциональных схем образующих его блоков, построенных на заданной элементной базе - микропроцессорном комплекте и элементах серий ТТЛ, БИС ОЗУ и ПЗУ.

Операционный блок получается соединением  $N_{\text{ппэ}} = n/2$  центральных процессорных элементов серии К589 и из  $N_{\text{ппэ}} = n/4$  элементов серии К1804. При этом в случае серии К589 образуются две  $n$  – разрядные выходные шины – адреса и данных, являющиеся выходами соответствующих регистров с  $z$  – состоянием.

Как образуются  $n$  – разрядные обработчики из секций ЦПЭ, можно узнать из раздела 3. Здесь также не обсуждается вопрос построения памяти из выбранных БИС ОЗУ и ПЗУ.

Операционный блок из ЦПЭ серии К1804 имеет одну выходную шину. Для образования другой – адресной шины необходим  $n$  – разрядный регистр-защёлка адреса. Естественно, в формате микрокоманды предусматривается разряд для задания микрооперации «Приём в регистр адреса».

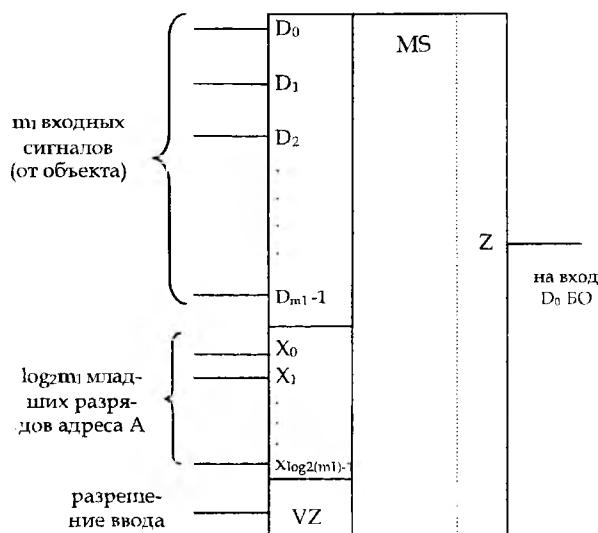

Блок ввода представляет собой мультиплексор с  $m_1$  информационными входами  $D_0 \div D_{m_1 - 1}$  и  $\log_2 m_1$  управляющих входов (рис. 1.4). Наличие входа выборки  $VZ$  и способ формирования сигнала «Разрешение ввода» зависит от типа архитектуры и адресации ПДЭ (см. таблицу 1.1), а также и от выбранного способа подключения мультиплексора к операционному блоку.

Рис. 1.4. Функциональная схема блока ввода

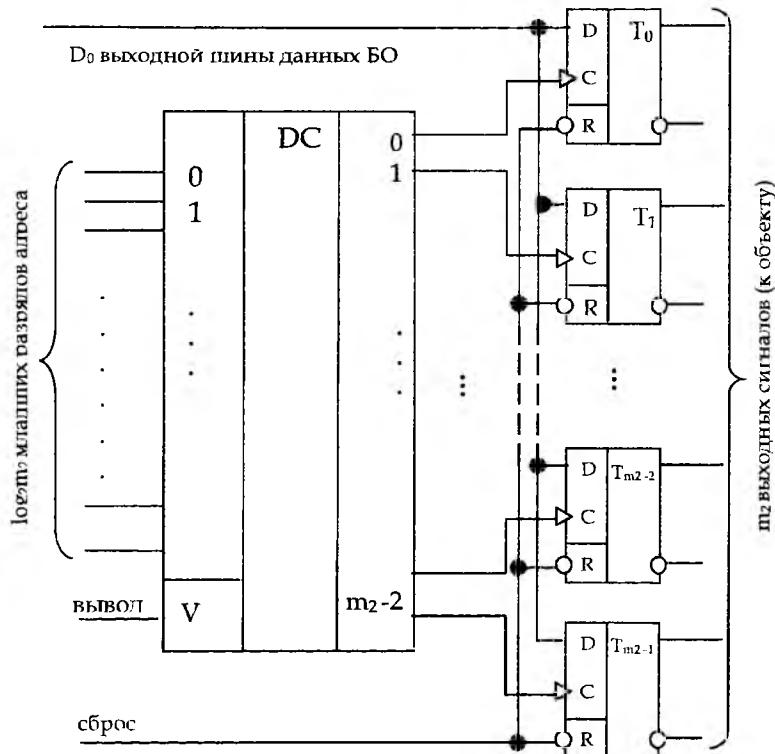

Блок вывода (рис. 1.5) состоит из  $m_2$  триггеров  $T_0 - T_{m_2-1}$ , являющихся собственно выходными портами ПЛК, и дешифратора с  $m_2$  выходами. Последний является, по сути дела, демультиплексором сигнала «вывод», формирование которого определяется заданной архитектурой ПЛК. В качестве сигнала «сброс» рациональнее всего использовать сигнал начальной установки адреса микрокоманды в УБ (или отдельную МКО).

Рис. 1.5. Функциональная схема блока вывода

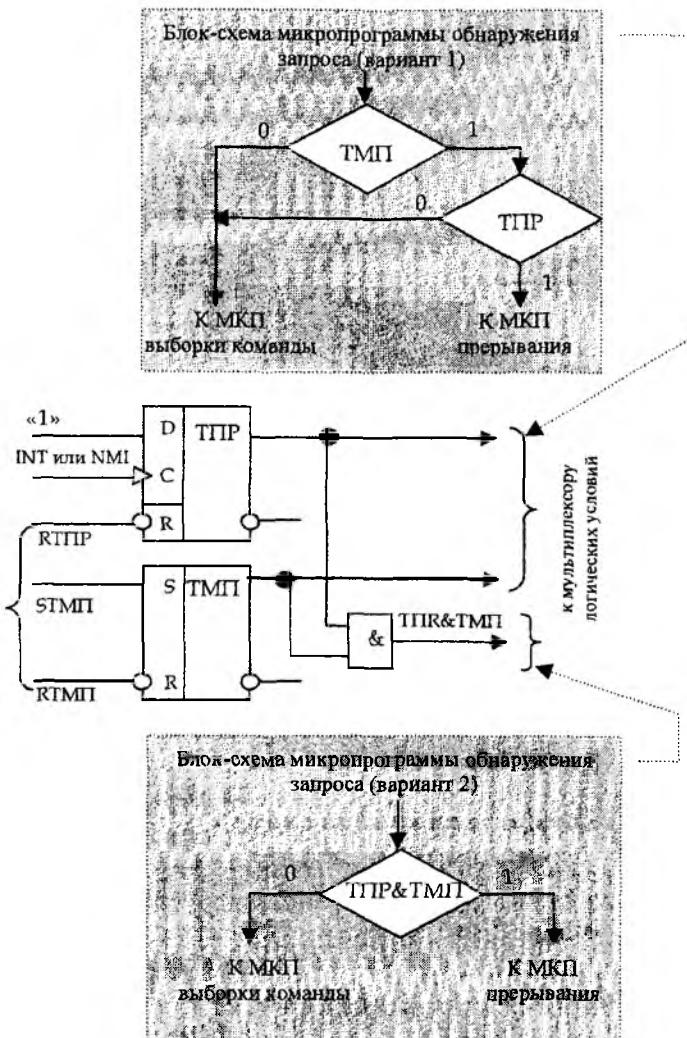

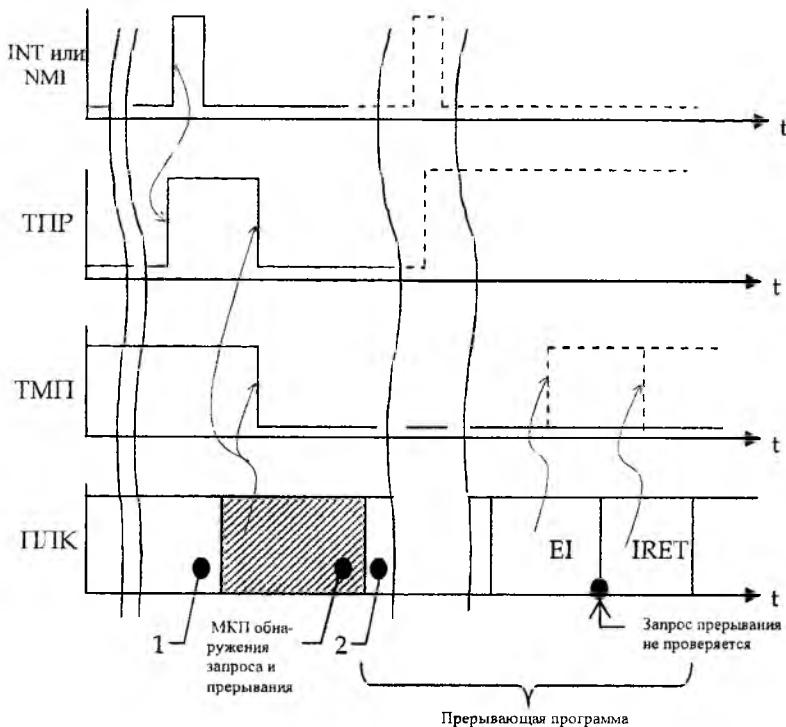

Блок прерываний (БП), не смотря на простоту своей схемы, требует более детального описания. Он состоит из двух триггеров (рис.1.6): триггера прерываний ТПР и триггера маски прерываний ТМП. Первый служит для запоминания запроса прерывания (INT или NMI), представляющего собой короткий импульс (рис 1.7). Триггер маски является программно доступным элементом (в командах EI и DI) в случае маскируемого запроса прерывания INT. В случае немаскируемого прерывания, он служит для исключения повторного прерывания в случае появления NMI во время выполнения прерывающей программы.

Обнаружение запроса прерывания осуществляется либо по осведомительным сигналам с выходов триггеров ТПР и ТМП (вариант 1, конъюнктор в схеме рис.1.6 отсутствует), либо по сигналу логического условия ТПР&ТМП при наличии конъюнктора (вариант 2). Выбор способа определяется разработчиком.

На рис.1.7 цифрой 1 обозначена команда основной программы (программы управления объектом), после которой наступает прерывание, а цифрой 2 – первая команда прерывающей команды. Сброс триггеров ТПР, ТМП осуществляется в процессе исполнения МКП прерывания. Завершающая часть прерывающей программы имеет следующие особенности:

- в случае маскируемого запроса восстановление состояния ТМП выполняет МКП команды EI, причём переход осуществляется к МКП выборки команды (см. пунктир на рис.1.3). Тем самым гарантируется выполнение последней команды прерывающей программы – команды IRET;

- в случае немаскируемого прерывания команда EI отсутствует, а установку в единицу триггера маски выполняет МКП команды IRET.

из микрокоманды

Рис. 1.6. Функциональная схема блока прерывания

Рис. 1.7. Временная диаграмма процесса прерывания.

В таблице 1.3 показано, в каких точках микропрограммы рабочего цикла ПЛК происходит сброс и восстановление состояний триггеров ТПР и ТМП.

Микропрограмма прерывания требует формирования адресов ячеек ПД для сохранения состояния РС, А и R и адреса начала прерывающей программы. Чтобы не использовать микроконстанту и не усложнять устройство, рационально сохранять регистры в последних ячейках ПД. Адресом начала прерывающей программы удобно сделать адрес  $C_{пп} - 1$ , расположив в ней команду перехода на фактическое начало этой программы.

Таблица 1.3

Манипуляции с ТПР и ТМП

| Запрос прерывания             | Триггер прерывания ТПР                              |                 | Триггер маски прерывания ТМП                                               |                                                     |

|-------------------------------|-----------------------------------------------------|-----------------|----------------------------------------------------------------------------|-----------------------------------------------------|

|                               | Установка в «0»                                     | Установка в «1» | Установка в «0»                                                            | Установка в «1»                                     |

| INT<br>(маскируемый запрос)   | 1) в МКП начальной установки<br>2) в МКП прерывания | сигналом INT    | 1) в МКП начальной установки<br>2) в МКП команды DI<br>3) в МКП прерывания | в МКП команды EI                                    |

| NMI<br>(немаскируемый запрос) | 1) в МКП начальной установки<br>2) в МКП прерывания | сигналом NMI    | в МКП прерывания                                                           | 1) в МКП начальной установки<br>2) МКП команды IRET |

При разработке функциональной схемы ПЛК определяется полное множество входных сигналов УБ (включая логические условия, внешние сигналы и разряды кода операции команды) и набор сигналов микроопераций и кодов, требуемых для управления блоками процессора, (то есть формат микрокоманды). Здесь могут быть полезны сведения из [3].

Операционная часть микрокоманды включает поле управляющего кода и бит входного переноса для операционного блока, поле маски (в случае K589), биты микроопераций для памяти и блоков ввода, вывода и прерываний.

Адресная часть микрокоманды содержит поля задания способа перехода, адреса следующей микрокоманды и управления мультиплексором логических условий в УБ. Суммарное число разрядов операционной и адресной частей микрокоманды определяет разрядность ячеек памяти микрокоманд  $n_{\text{имк}}$

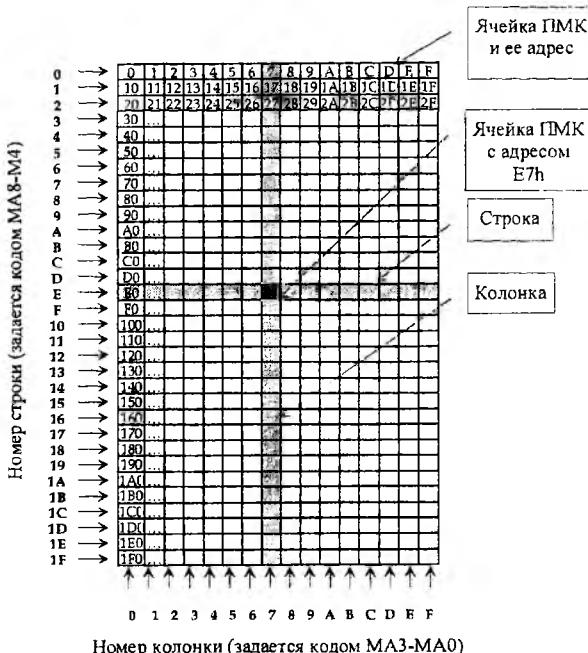

Емкость памяти микрокоманд  $C_{\text{пмк}}$  в УБ определяется после разработки микропрограмм ПЛК. Последние представляются двумя способами:

- в виде содержательных граф – схем алгоритмов (ГСА) для каждого блока в микропрограмме рабочего цикла ПЛК;

- в виде таблиц «адрес – содержимое ячейки», т.е. в виде кодированных микропрограмм. Общее число строк в этих таблицах, дополненной до ближайшего числа, кратного целой степени 2, есть ёмкость ПМК. После этого возможны корректировка адресной части микрокоманды в сторону уменьшения числа её разрядов и, следовательно, упрощение схемы УБ.

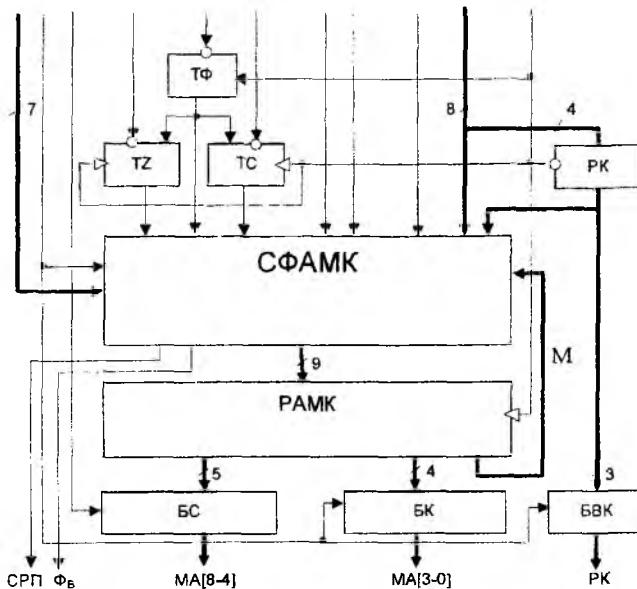

Управляющий блок разрабатывается с использование раздела 3 настоящих методических указаний или [4, 5, 6]. Он состоит из:

- памяти микрокоманд (ПМК), объёмом  $C_{\text{пмк}} \times n_{\text{пмк}}$  бит;

- БИС блоков микропрограммного управления (БМУ);

- регистра адреса РАМК или информационного регистра РИМК (могут отсутствовать);

- мультиплексора логических условий;

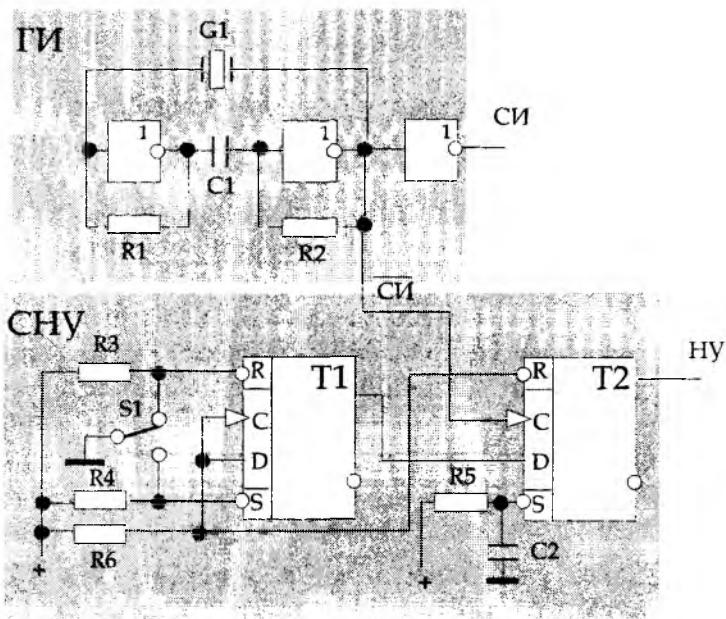

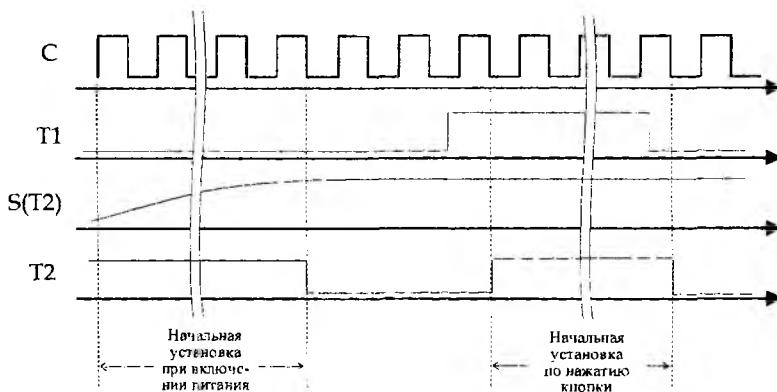

- узла синхронизации и начальной установки (УСНУ).

Блок микропрограммного управления в серии К589 формирует девятиразрядный адрес микрокоманды и адресует память ёмкостью 512 ячеек. Этого количества достаточно для размещения микропрограмм ПЛК. В серии К1804 один блок (секция) БМУ формирует четырехразрядный адрес, поэтому необходимо соединение двух БМУ для адресации памяти микрокоманд ёмкостью до 256 ячеек.

Мультиплексор логических условий служит коммутатором осведомительных сигналов, формируемых блоком обработки, блоком прерываний и переключателем режимов S.

Функциональная схема УСНУ – общая для двух тем проекта - приведена в разделе 4 данных методических указаний.

### **Разработка принципиальной схемы устройства и выбор параметров импульса синхронизации.**

Рекомендации по использованию заданной элементной базы при разработке принципиальных схем приведены в разделе 3 данных методических указаний. Особенностью принципиальной схемы ПЛК является наличие двух электрических соединителей (разъемов): одного - для связи с объектом управления и другого - для соединения с блоком питания.

## 2. Сопроцессор с архитектурой RISC

### 2.1. Общие сведения о проектируемом устройстве.

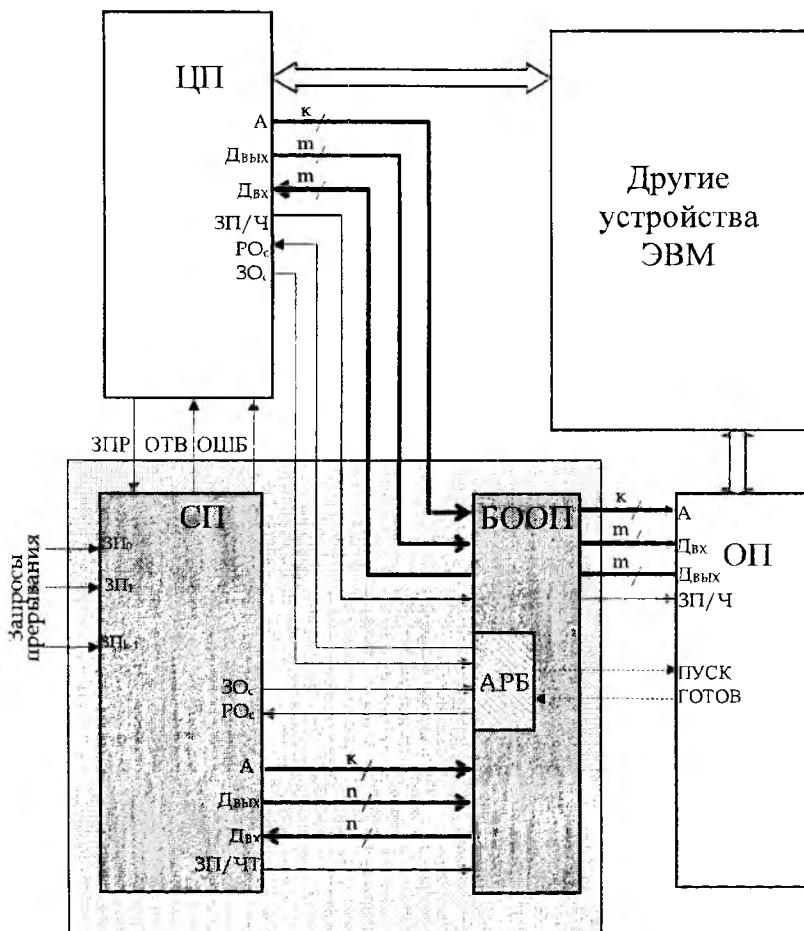

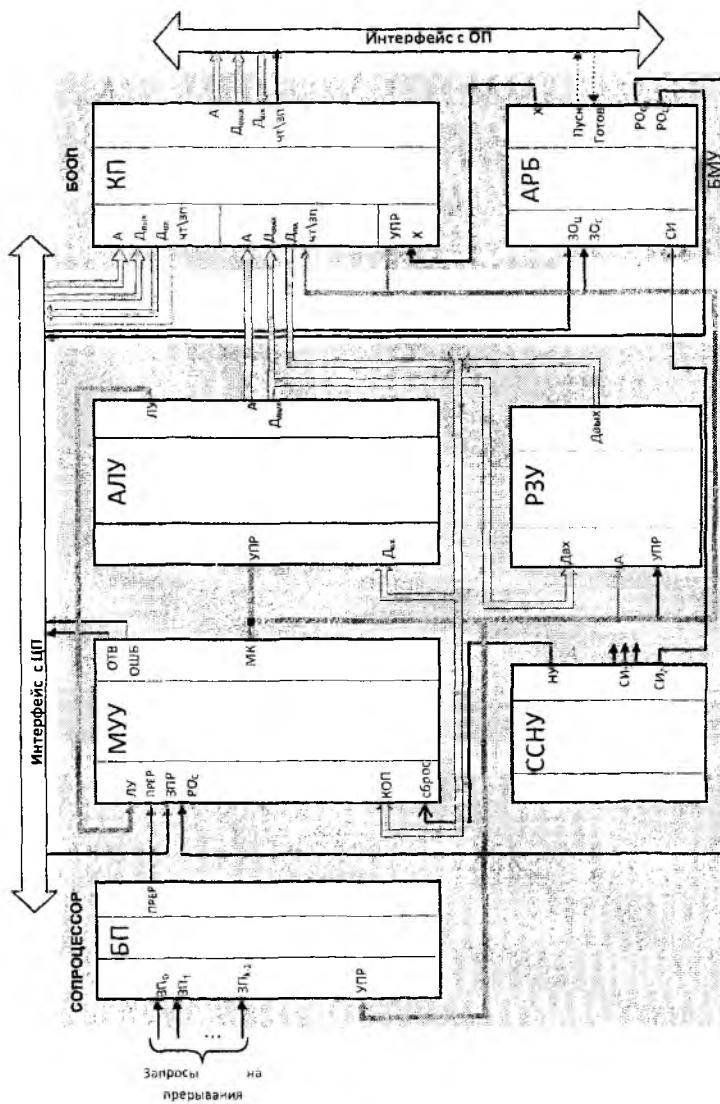

Структурная схема подключения сопроцессора (СП) приведена на рис. 2.1.

Рис.2.1. Структурная схема подключения СП

Сопроцессор (СП) функционирует параллельно с центральным процессором ЦП и использует общую с ЦП оперативную память (ОП). Для организации обращений двух процессоров в общую ОП используется блок обращений в ОП (БООП), в состав которого входит арбитр (АРБ) для разрешения конфликтов при одновременных обращениях процессоров.

Для взаимодействия устройств СП используются следующие сигналы и шины:

|                      |                                                 |

|----------------------|-------------------------------------------------|

| ЗПР                  | - сигнал запуска СП в работу,                   |

| ОТВ                  | - сигнал подтверждения запуска от СП,           |

| ОШБ                  | - сигнал от СП об обнаружении ошибки,           |

| $ЗП_0 \div ЗП_{k-1}$ | - запросы прерывания,                           |

| А                    | - адресная шина,                                |

| Двых                 | - выходная шина данных,                         |

| Двх                  | - входная шина данных,                          |

| ЗП/ЧТ                | - сигналы управления режимами записи/чтения ОП, |

| Пуск,                | - сигналы управления ОП.                        |

| Готов                |                                                 |

Каждый из процессоров реализует собственную систему команд и работает по своей программе, находящейся в ОП. Для обращении в ОП процессоры формируют k-разрядный адрес, сигналы управления режимами записи/чтения (ЗП/ЧТ) и выставляют запрос на обращение, передаваемый в арбитр (ЗО<sub>С</sub> от СП и ЗО<sub>Ц</sub> от ЦП). Обращение в ОП разрешается при получении от арбитра сигнала разрешения (РО<sub>С</sub> для СП и РО<sub>Ц</sub> для ЦП). Обмен данными между СП и БООП выполняется по n-разрядным шинам, а между БООП и ОП по m-разрядным шинам.

Алгоритм работы СП, реализуемый на микропрограммном уровне, представлен на рис 2.2. Запуск СП в режим исполнения программы осуществляется ЦП выдачей сигнала ЗПР. После получения ЗПР=1 СП выдает сигнал

$OTB=1$  и осуществляет загрузку своих регистров начальными состояниями (предварительно оговоренными или загружаемыми из фиксированной области ОП значениями). Далее СП ожидает от ЦП сброса сигнала ЗПР=0. Для ис-

Рис.2.2. Укрупненный алгоритм работы СП

ключения “зависания” в этом состоянии в СП на микропрограммном уровне запускается таймер для ограничения времени ожидания. При отсутствии ЗПР=0 более  $T_{\text{пред}}$  СП выдает сигналы ОШБ=1, ОТВ=0 и возвращается в начальное состояние ожидания запуска. В противном случае после получения ЗПР=0 СП переходит к реализации программы, размещенной в ОП путем повторения машинного цикла исполнения команд. Выход из программы осуществляется при обнаружении признака «конец программы» (может формироваться специальной командой СП или сравнением программного счетчика с заданным конечным значением), после чего СП формирует сигнал ОТВ =0 и переходит в начальное состояние ожидания запуска. При возникновении ошибок в процессе исполнения программы СП выходит из машинного цикла и сообщает об этом в ЦП сигналаами ОШБ=1, ОТВ =0.

## 2.2. Программистская модель СП

Система команд разрабатываемого СП является подмножеством систем команд микропроцессоров серии K580 (i8080) или K1810 (i8086). Такая система является функционально полной для СП, однако включает только основные команды из базовых систем команд с упрощенными форматами и способами адресации. ЭВМ, реализующие подобные системы команд, получили название RISC (Reduced Instruction Set Computers). В СП с архитектурой K580 (i8080) все команды имеют формат длиной один байт (трехбайтные команды JC, CALL заменяются на однобайтные заданием адреса перехода в регистровой паре HL), а в СП с архитектурой K1810 (i8086) используются только двухбайтные команды (однобайтная команда RET преобразуется в двухбайтную добавлением нулевого байта).

Программистская модель СП должна включать все программно-доступные регистры базовых моделей микропроцессоров K580 (i8080) или K1810 (i8086). В таблице 2.1 приведены два варианта систем команд СП с использованием мнемоники команд, принятой в описаниях соответствующих микропроцессоров. Описания систем команд можно найти в литературе [7,8].

Таблица 2.1

Варианты системы команд

| K580 (i8080)                                                                                  | K1810 (i8086)                                                                                                      |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| MOV R1,R2;<br>MOV R,M; MOV M,R;<br>PUSH RP;<br>POP RP                                         | MOV reg,r/m; MOV r/m, reg;<br>MOV sr,r/m; MOV r/m, sr (sr≠CS);<br>PUSH r/m; PUSH F ;<br>POP r/m; POP F;            |

| ADC R; SBB R;<br>INC R; DCR R; INX RP;<br>CMP R;                                              | ADC reg,r/m; SBB reg,r/m;<br>INC r/m; DCR r/m;<br>CMP reg,r/m                                                      |

| ANA R; XRA R; ORA R;<br>CMA;                                                                  | AND reg r/m; XOR reg,r/m;<br>OR reg,r/m;<br>NOT r/m;                                                               |

| RAL; RAR;                                                                                     | RCL r/m,CL; RCR r/m,CL;<br>SHL r/m,CL; SHR r/m,CL;<br>SAR r/m,CL                                                   |

| PCHL;<br>JC (по адресу в HL)<br>(C= Z, NZ, C, NC);<br>CALL(по адресу в HL);<br>RST n;<br>RET; | JMP WORD r/m; JMP DWORD<br>r/m<br>JC (C= Z, NZ, C, NC, S, NS, O,<br>NO);<br>CALL WORD r/m; CALL<br>DWORD r/m; RET; |

| STC; CMC                                                                                      | CLC; STC; CMC                                                                                                      |

| -                                                                                             | md=11;<br>md=00 при r/m≠110                                                                                        |

## **2.3. Структурная организация СП и БООП**

### ***2.3.1 Основные блоки СП, БООП и их подключение***

Обобщенная структурная схема СП и БООП представлена на рис.2.3. В состав СП входят блоки, перечисленные табл. 2.2. Организация каждого из перечисленных на схеме блоков определяется вариантом задания.

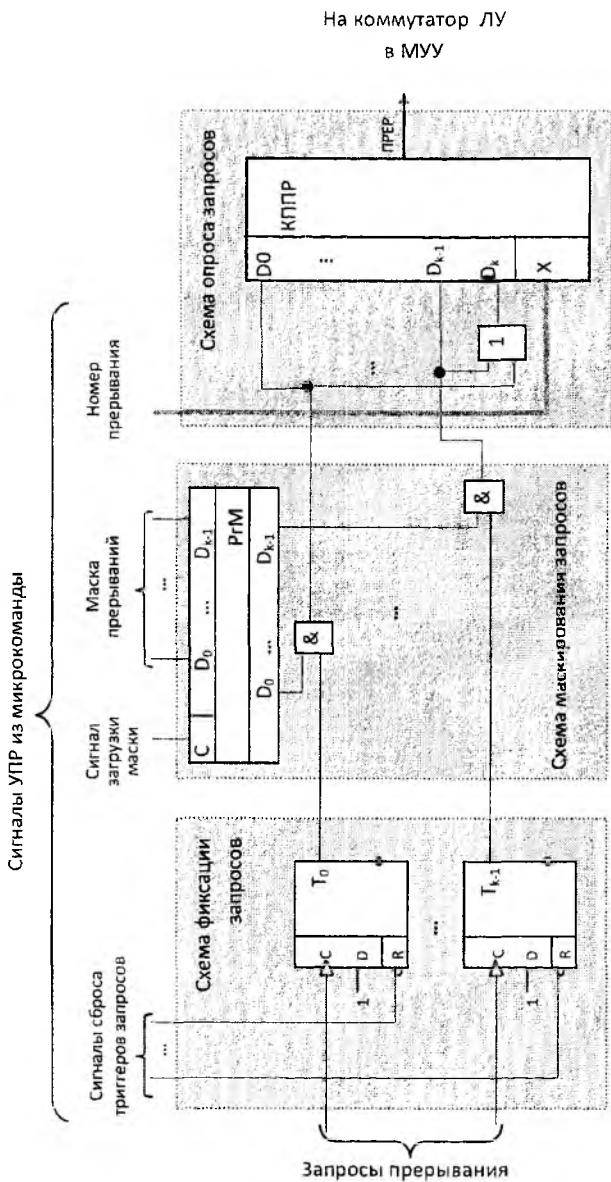

### ***2.3.2. Организация системы прерывания СП***

На рис. 2.4 приведена обобщенная структурная организация БП с микропрограммным опросом запросов на прерывание  $Z\Pi_0, \dots, Z\Pi_{k-1}$  через коммутатор КППР, подключаемый к коммутатору логических условий в составе МУУ. Основные функции системы прерываний реализуются при этом на микропрограммном уровне.

Прерывания могут быть вызваны либо уровнем (статическая фиксация), либо по фронту (динамическая фиксация) сигнала запроса. Для динамической фиксации может быть использован вариант схемы, приведенный на рис 2.4.

Система приоритетов прерывающих программ реализуется с использованием маскирования.

В проекте реализуются следующие варианты прерывающих процедур:

1. Задержка в работе СП на заданное время с возвратом к прерванной программе.

2. Загрузка в фиксированную область ОП значений заданных программно-доступных регистров СП.

3. Задержка в работе СП на заданное время с переходом в исходное состояние.

Рис. 2.3 Обобщенная структурная схема СП и БОП

## Блоки в составе СП

Таблица 2.2

|             |                                                  |                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>МУУ</b>  | <b>Микропрограммное устройство управления</b>    | ЛУ - логические условия (признаки) из АЛУ<br>КОП - код операции команды, принимаемых из ОП<br>ЭИР, СТВ, ОШБ - сигналы взаимодействия с ЦП<br>ПРЕР - сигнал разрешения прерывания от блока прерываний<br>Сброс - сигнал начальной установки процессора<br>МК - операционная часть микрокомпьютера<br>РО <sub>1</sub> - сигнал разрешения обращения в ОП |

| <b>АЛУ</b>  | <b>Арифметико-логическое устройство</b>          | Дж.Дых - входные и выходные шины данных<br>А - адресная шина в ОП<br>УПР-шина выбора функции АЛУ<br>ЛУ-логические условия (признаки)                                                                                                                                                                                                                   |

| <b>РЗУ</b>  | <b>Регистровое ЗУ</b>                            | Дж.Дых - входные и выходные шины данных.<br>А - адресная шина.<br>УПР - управление памятью памяти запись/чтение/запись отключения и др.).<br>ЗП <sub>0</sub> -ЗП <sub>k-1</sub> - запросы на прерывания.<br>УПР - шина управления БП (маска, сброс триггеров запросов, номер запроса и др.).                                                           |

| <b>БП</b>   | <b>Блок прерываний</b>                           | СЧ <sub>1</sub> , СЧ <sub>2</sub> - сигналы синхронизации работы блоков СП и БОП.<br>НУ - сигнал сброса СП в начальное состояние.                                                                                                                                                                                                                      |

| <b>СЧНУ</b> | <b>Схема синхронизации и начальной установки</b> | ЭО <sub>1</sub> , ЭО <sub>2</sub> - запросы на обращение в ОП от ЦП и СП.<br>Х - сигнал управления КП.<br>РО <sub>11</sub> , РО <sub>12</sub> - разрешение обращения в ОП для ЦП и СП.<br>Пуск, Готов - квантующие сигналы организаций асинхронной работы ОП                                                                                           |

| <b>АРБ</b>  | <b>Арбитр, управляющий доступом в ОП</b>         | А - адресная, Д <sub>вход</sub> /Д <sub>выход</sub> - выходная/входная, ЧТ/ЗП - управляющая шины                                                                                                                                                                                                                                                       |

| <b>КП</b>   | <b>Коммутатор шин</b>                            |                                                                                                                                                                                                                                                                                                                                                        |

Рис.2.4 Структурная схема блока прерываний

Реализация прерывающих процедур выполняется на программном уровне в виде прерывающей программы.

Ниже приведена таблица 2.3 с вариантами организации системы прерываний, используемыми в проекте.

Таблица 2.3

Варианты организации системы прерываний

| № варианта | статическая\ динамическая фиксация запросов | наличие маскирования | прерывающая процедура |

|------------|---------------------------------------------|----------------------|-----------------------|

| 1          | стат                                        | нет                  | 1 (по ЗП0)            |

| 2          | стат                                        | нет                  | 2 (по ЗП1)            |

| 3          | дин                                         | нет                  | 3 (по ЗП3)            |

| 4          | дин                                         | нет                  | 1 (по ЗП2)            |

| 5          | стат                                        | да                   | 1 (по ЗП0)            |

| 6          | стат                                        | да                   | 2 (по ЗП1)            |

| 7          | дин                                         | да                   | 3 (по ЗП3)            |

| 8          | дин                                         | да                   | 1 (по ЗП2)            |

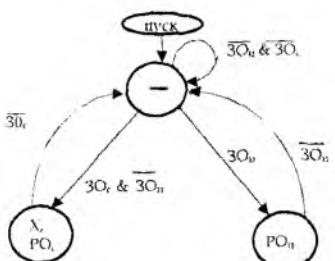

### 2.3.3. Организация арбитража ОП

СП и ЦП осуществляют обращения к ОП через общий коммутатор адресных, информационных и управляющих шин, входящий в состав БООП. Для разрешения конфликтов при их одновременных обращениях в состав БООП включен арбитр, на входы которого подаются запросы на обращения в ОП от двух процессоров. Арбитр управляет работой коммутатора и формирует сигналы разрешения обращений для СП и ЦП. Схема арбитра определяется способом взаимодействия процессоров с ОП. Варианты организации арбитра приведены в виде графа смены состояний на рис 2.5. Во всех вариантах большим приоритетом обладает ЦП.

1. Отсчет времени обращения с учетом заданной максимальной длительности цикла обращения в ОП осу-

ществляется средствами процессора (рис. 2.5а). После получения от процессоров запросов арбитр в соответствии с присвоенными приоритетами выдает сигнал разрешения (РО) одному из процессоров и сигнал X для его подключения к ОП. Подключенный процессор занимает ОП и отсчитывает на микропрограммном уровне время готовности ОП, после чего завершает процедуру обращения и сбрасывает сигнал запроса.

2. Отсчет времени обращения с учетом заданной максимальной длительности цикла обращения в ОП осуществляется средствами арбитра (рис. 2.5б). Для отсчета времени обращения в состав арбитра включен таймер (счетчик тактов синхронизации арбитра). После получения от процессоров запросов арбитр в соответствии с присвоенными приоритетами подключает шины одного из процессоров к ОП (по сигналу X) и одновременно запускает таймер. После срабатывания таймера (по сигналу  $\alpha$ ) выдается разрешение РО подключенному процессору, который завершает цикл обращения и сбрасывает запрос.

3. Арбитр реализует асинхронный способ обращения в ОП, при котором отсчет фактической длительности обращения осуществляется в ОП. (рис. 2.5в). С этой целью введен сигнал ПУСК, выдаваемый арбитром в ОП после подключения к ОП одного из процессоров. После завершения цикла ОП отвечает арбитру сигналом ГОТОВ, по которому арбитр формирует сигнал разрешения процессору. Процессор завершает цикл обращения и сбрасывает запрос.

## 2.4 Варианты заданий на проектирование СП.

Варианты заданий на курсовой проект приведены в таблице 2.4.

а) синхронный обмен с отсчетом максимального времени обращения в СП

в) асинхронный обмен с отсчетом фактического времени обращения в ОП.

б) синхронный обмен с отсчетом максимального времени обращения в АРБ

Рис. 2.5. Варианты организации арбитра

Таблица 2.3.

## Варианты заданий

| №<br>вар | Систе-<br>ма<br>команд<br>1-K580<br>2-K1810 | АЛУ                |                  | МУУ                    |                               |                                        |

|----------|---------------------------------------------|--------------------|------------------|------------------------|-------------------------------|----------------------------------------|

|          |                                             | Элементная<br>база | Разряд-<br>ность | Элементная<br>база БМУ | Элемен-<br>тая<br>база<br>ПМК | Команда для микропро-<br>граммирования |

| 1.       | 1                                           | K1804BC1           | 8                | K1804BV1               | K541                          | MOV R1,R2                              |

| 2.       | 1                                           | K1804BC2           | 8                | K1804BV2               | K573                          | MOV R,M                                |

| 3.       | 1                                           | K1804BC1           | 8                | K1804BV2               | K555                          | MOV M,R                                |

| 4.       | 1                                           | K1804BC2           | 8                | K1804BV1               | K541                          | PUSH RP                                |

| 5.       | 1                                           | K589ИK02           | 8                | K589ИK01               | K573                          | POP RP                                 |

| 6.       | 1                                           | K1804BC1           | 8                | K589ИK01               | K555                          | ADC R                                  |

| 7.       | 1                                           | K1804BC2           | 8                | K589ИK01               | K541                          | SBB R                                  |

| 8.       | 1                                           | K589ИK02           | 8                | K1804BV1               | K573                          | INC R                                  |

| 9.       | 1                                           | K589ИK02           | 8                | K1804BV2               | K555                          | DCR R                                  |

| 10.      | 2                                           | K1804BC1           | 8                | K1804BV1               | K541                          | MOV reg,r/m                            |

| 11.      | 2                                           | K1804BC2           | 8                | K1804BV2               | K573                          | MOV r/m, reg                           |

| 12.      | 2                                           | K1804BC1           | 8                | K1804BV2               | K555                          | MOV sr,r/m                             |

| 13.      | 2                                           | K1804BC2           | 8                | K1804BV1               | K541                          | MOV r/m, sr                            |

| 14.      | 2                                           | K589ИK02           | 8                | K589ИK01               | K573                          | PUSH r/m                               |

| 15.      | 2                                           | K1804BC1           | 8                | K589ИK01               | K555                          | PUSH F                                 |

| 16.      | 2                                           | K1804BC2           | 8                | K589ИK01               | K541                          | POP r/m                                |

| 17.      | 2                                           | K589ИK02           | 8                | K1804BV1               | K573                          | POP F                                  |

| 18.      | 2                                           | K589ИK02           | 8                | K1804BV2               | K555                          | ADC reg,r/m                            |

| 19.      | 1                                           | K1804BC1           | 16               | K1804BV1               | K541                          | JNX RP                                 |

| 20.      | 1                                           | K1804BC2           | 16               | K1804BV2               | K573                          | CMP R                                  |

| 21.      | 1                                           | K1804BC1           | 16               | K1804BV2               | K555                          | ANAR                                   |

| 22.      | 1                                           | K1804BC2           | 16               | K1804BV1               | K541                          | XRA R                                  |

| 23.      | 1                                           | K589ИK02           | 16               | K589ИK01               | K573                          | ORA R                                  |

| 24.      | 1                                           | K1804BC1           | 16               | K589ИK01               | K555                          | CMA                                    |

| 25.      | 1                                           | K1804BC2           | 16               | K589ИK01               | K541                          | RAL                                    |

| 26.      | 1                                           | K589ИK02           | 16               | K1804BV1               | K573                          | RAR                                    |

| 27.      | 1                                           | K589ИK02           | 16               | K1804BV2               | K555                          | CALL                                   |

| 28.      | 2                                           | K1804BC1           | 16               | K1804BV1               | K541                          | SBB reg,r/m                            |

| 29.      | 2                                           | K1804BC2           | 16               | K1804BV2               | K573                          | INC r/m                                |

| 30.      | 2                                           | K1804BC1           | 16               | K1804BV2               | K555                          | DCR r/m                                |

| 31.      | 2                                           | K1804BC2           | 16               | K1804BV1               | K541                          | CMP reg,r/m                            |

| 32.      | 2                                           | K589ИK02           | 16               | K589ИK01               | K573                          | JMP WORD r/m                           |

| 33.      | 2                                           | K1804BC1           | 16               | K589ИK01               | K555                          | JMP DWORD r/m                          |

| 34.      | 2                                           | K1804BC2           | 16               | K589ИK01               | K541                          | CALL WORD r/m                          |

| 35.      | 2                                           | K589ИK02           | 16               | K1804BV1               | K573                          | CALL DWORD r/m                         |

| 36.      | 2                                           | K589ИK02           | 16               | K1804BV2               | K555                          | JC                                     |

Таблица 2.3

## Варианты заданий (продолжение)

| №<br>вар | БП | БОП          |                     |                                   |                                            |                                   |     |

|----------|----|--------------|---------------------|-----------------------------------|--------------------------------------------|-----------------------------------|-----|

|          |    | Вари-<br>ант | Тип<br>арбит-<br>ра | Разрядность<br>информационных шин | Совмещен-<br>ность информа-<br>ционных шин | Разряд-<br>ность адресной<br>шины |     |

| 1.       | 1  | 2            |                     | 16                                | нет                                        | 16                                | 0,5 |

| 2.       | 2  | 1            |                     | 16                                | да                                         | 16                                | 1,0 |

| 3.       | 3  | 2            |                     | 16                                | да                                         | 16                                | 0,7 |

| 4.       | 4  | 3            |                     | 16                                | нет                                        | 16                                | 1,0 |

| 5.       | 5  | 1            |                     | 8                                 | нет                                        | 16                                | 0,4 |

| 6.       | 6  | 2            |                     | 8                                 | да                                         | 16                                | 0,3 |

| 7.       | 7  | 3            |                     | 8                                 | да                                         | 16                                | 0,8 |

| 8.       | 8  | 1            |                     | 8                                 | нет                                        | 16                                | 0,5 |

| 9.       | 1  | 2            |                     | 8                                 | нет                                        | 16                                | 0,6 |

| 10.      | 2  | 3            |                     | 16                                | да                                         | 20                                | 0,8 |

| 11.      | 3  | 1            |                     | 16                                | да                                         | 20                                | 0,6 |

| 12.      | 4  | 2            |                     | 16                                | нет                                        | 20                                | 0,4 |

| 13.      | 5  | 2            |                     | 16                                | нет                                        | 20                                | 0,5 |

| 14.      | 6  | 1            |                     | 8                                 | да                                         | 20                                | 1,0 |

| 15.      | 7  | 2            |                     | 8                                 | да                                         | 20                                | 0,7 |

| 16.      | 8  | 3            |                     | 8                                 | нет                                        | 20                                | 1,0 |

| 17.      | 1  | 1            |                     | 8                                 | нет                                        | 20                                | 0,4 |

| 18.      | 2  | 2            |                     | 8                                 | нет                                        | 20                                | 0,3 |

| 19.      | 3  | 3            |                     | 16                                | нет                                        | 16                                | 0,8 |

| 20.      | 4  | 1            |                     | 16                                | да                                         | 16                                | 0,5 |

| 21.      | 5  | 2            |                     | 16                                | да                                         | 16                                | 0,6 |

| 22.      | 6  | 3            |                     | 16                                | нет                                        | 16                                | 0,8 |

| 23.      | 7  | 1            |                     | 8                                 | нет                                        | 16                                | 0,6 |

| 24.      | 8  | 2            |                     | 8                                 | да                                         | 16                                | 0,4 |

| 25.      | 1  | 3            |                     | 8                                 | да                                         | 16                                | 0,4 |

| 26.      | 2  | 1            |                     | 8                                 | нет                                        | 16                                | 0,5 |

| 27.      | 3  | 2            |                     | 8                                 | нет                                        | 16                                | 1,0 |

| 28.      | 4  | 3            |                     | 16                                | да                                         | 20                                | 0,7 |

| 29.      | 5  | 1            |                     | 16                                | да                                         | 20                                | 1,0 |

| 30.      | 6  | 2            |                     | 16                                | нет                                        | 20                                | 0,4 |

| 31.      | 7  | 3            |                     | 16                                | нет                                        | 20                                | 0,3 |

| 32.      | 8  | 1            |                     | 16                                | да                                         | 20                                | 0,8 |

| 33.      | 1  | 2            |                     | 16                                | да                                         | 20                                | 0,5 |

| 34.      | 2  | 3            |                     | 16                                | нет                                        | 20                                | 0,6 |

| 35.      | 3  | 1            |                     | 16                                | нет                                        | 20                                | 0,5 |

| 36.      | 4  | 2            |                     | 16                                | нет                                        | 20                                | 0,6 |

### **3. Элементная база для построения процессоров**

Процессор может быть реализован в виде одной интегральной схемы (однокристальный микропроцессор) либо с использованием стандартных комплектов интегральных схем, отличающихся быстродействием, энергопотреблением, степенью интеграции и другими параметрами (многокристальный микропроцессор). В данном проекте выбран второй вариант.

В состав комплектов многокристальных микропроцессоров входят два основных типа БИС:

- центральный процессорный элемент (ЦПЭ) для построения секционированных АЛУ,

- блок микропрограммного управления (БМУ) для построения устройств управления процессоров.

Ниже приводятся краткие описания БИС ЦПЭ и БМУ используемых в проекте серий.

#### **3.1. Серия БИС на основе двухразрядных ЦПЭ (серия К589)**

##### **3.1.1. БИС ЦПЭ для построения АЛУ**

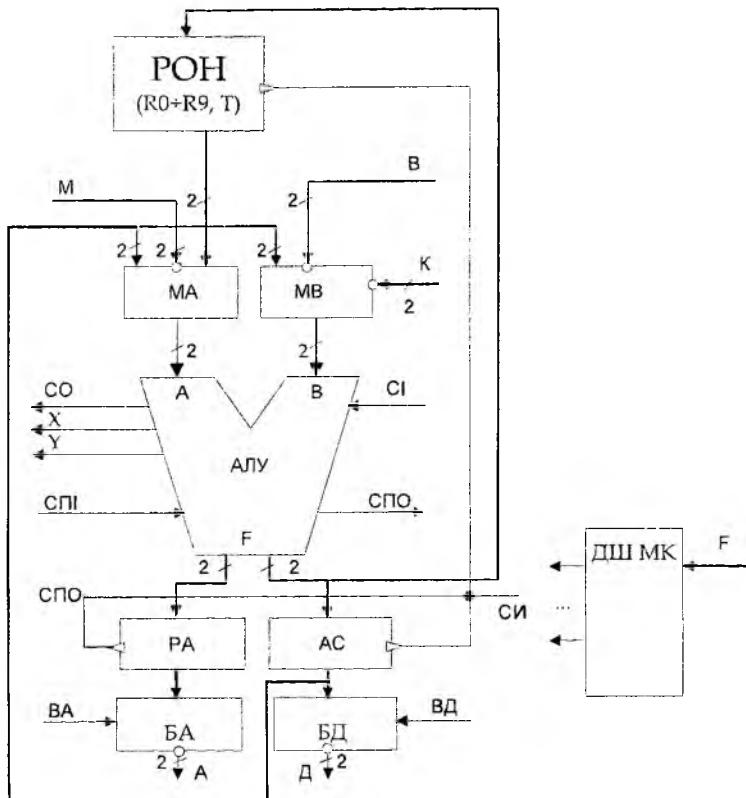

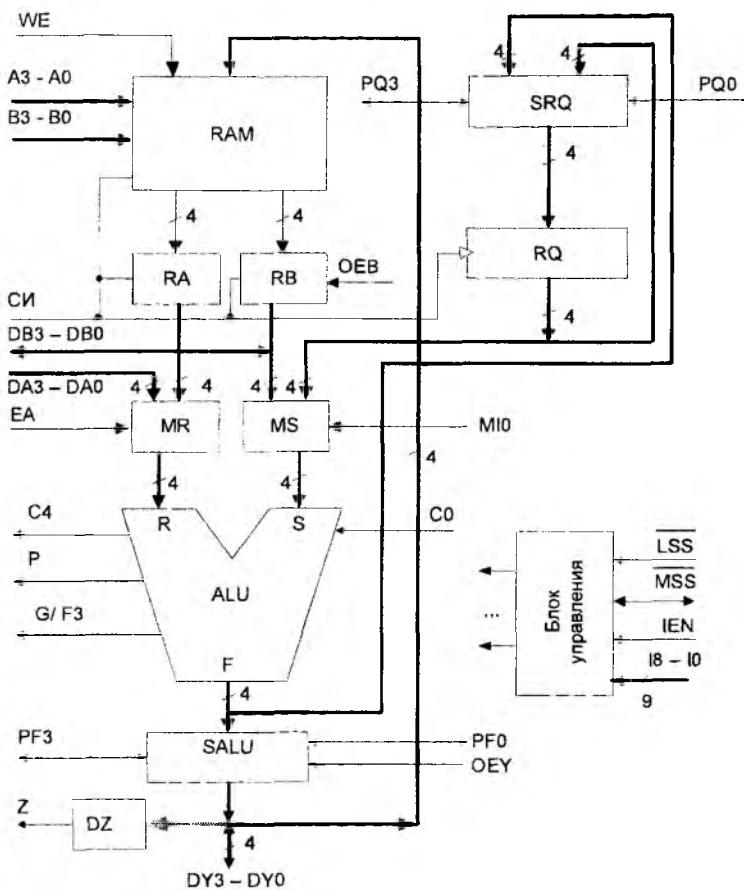

ЦПЭ представляет собой двухразрядную процессорную секцию, выполняющую функции арифметической и логической обработки двухразрядных операндов, их временного хранения и формирования различных признаков результатов. Структурная схема ЦПЭ приведена на рис.3.1. В состав ЦПЭ включены:

- двухразрядное комбинационное АЛУ,

- мультиплексоры входных operandов: МА на входе А и МВ на входе В АЛУ,

- блок регистров (РОН), включающий 10 регистров общего назначения R0 – R9 и регистр Т,

- вспомогательные регистры для временного хранения: регистр-аккумулятор данных (AC), регистр адреса (PA),

- буферы данных (БД) и адреса (БА) с тремя состояниями,

- дешифратор кода микроинструкций (ДШ МК) .

Рис. 3.1. Двухразрядная процессорная секция

Прием данных в ЦПЭ осуществляется по двум входным шинам: шине В, обычно используемой для приема информации из устройств ввода-вывода и ОЗУ данных, и шине М для приема адресной части команды из ОЗУ программ. Шина К предназначена для приема кода маски.

Выдача информации из ЦПЭ осуществляется по шине данных Д и шине адреса А. Выдача информации разрешается нулевым сигналом на управляющих входах ВА (выдача адреса) и ВД (выдача данных). Длястыковки с аналогичными модулями с целью наращивания разрядности обрабатываемых слов ЦПЭ имеет входы для переноса в 0-ой разряд (С1) и для приема информации в 1-ый разряд при сдвиге вправо (СП1), а также выходы переноса из 1-го разряда (СО) и выдачи информации из 0-го разряда при сдвиге вправо (СП0). Выходы СО и СП0 являются трехстабильными и взаимно блокированы, вследствие чего допускается их монтажное объединение с целью формирования общего сигнала. Синхронизация работы всех узлов ЦПЭ осуществляется подачей синхроимпульсов с периодом не менее 100 нс на вход СИ.

Выбор операции, реализуемой ЦДЭ, осуществляется семиразрядным кодом F [0÷6]. Старшие три бита кода F4, F5, F6 (код F) задают одну из восьми групп операций, выполняемых в АЛУ, а младшие биты F0 - F3 (код R ) - одну из трех операций в каждой группе F . Кроме этого код R определяет источники и приемники operandов, используемых в операциях ЦПЭ.

Выбор источника operandов по входу А АЛУ осуществляется мультиплексором МА, управляемым кодом R . В качестве таких источников могут служить: один из РОНов, входная шина М, регистр-аккумулятор АС. Выбор operandов по входу В АЛУ осуществляется мультиплексором МВ, причем источниками operandов могут быть регистр-аккумулятор АС или входная шина В. Код маски

с шины K позволяет осуществлять поразрядное маскирование операндов по входу В АЛУ.

Результат операции из комбинационного АЛУ заносится в один из следующих приемников: регистр адреса РА, регистр-аккумулятор АС или в один из РОНов. Выбор РОНа для записи результата осуществляется кодом R.

В зависимости от кода R в каждой группе операций, задаваемых кодом F, выделяются три вида операций, отличающихся операндами и типом операций. В таблице 3.1 представлены коды F для групп операций АЛУ. В таблице 3.2 представлены коды R и соответствующие им операнды, используемые в операциях ЦПЭ. В таблице 3.3 приведен полный перечень операций, выполняемых в ЦПЭ для произвольной маски K, для K=00 и для K=11.

Таблица 3.1

| Код F | F6 | F5 | F4 |

|-------|----|----|----|

| 0     | 0  | 0  | 0  |

| 1     | 0  | 0  | 1  |

| 2     | 0  | 1  | 0  |

| 3     | 0  | 1  | 1  |

| 4     | 1  | 0  | 0  |

| 5     | 1  | 0  | 1  |

| 6     | 1  | 1  | 0  |

| 7     | 1  | 1  | 1  |

Таблица 3.2

| F3 | F2 | F1 | F0 | Код R | Регистр |

|----|----|----|----|-------|---------|

| 0  | 0  | 0  | 0  |       | R0      |

| 0  | 0  | 0  | 1  |       | R1      |

| 0  | 0  | 1  | 0  |       | R2      |

| 0  | 0  | 1  | 1  |       | R3      |

| 0  | 1  | 0  | 0  |       | R4      |

| 0  | 1  | 0  | 1  |       | R5      |

| 0  | 1  | 1  | 0  | 1     | R6      |

| 0  | 1  | 1  | 1  | 1     | R7      |

| 1  | 0  | 0  | 0  |       | R8      |

| 1  | 0  | 0  | 1  |       | R9      |

| 1  | 1  | 0  | 0  |       | T       |

| 1  | 1  | 0  | 1  |       | AC      |

| 1  | 0  | 1  | 0  | 2     | T       |

| 1  | 0  | 1  | 1  | 2     | AC      |

| 1  | 1  | 1  | 0  | 3     | T       |

| 1  | 1  | 1  | 1  | 3     | AC      |

Таблица 3.3

Операции, выполняемые в ЦПЭ

| Код F | Код R | Операция<br>(маска K – произвольная)                                                 | Операция<br>(маска K = 11)                                               | Операция<br>(маска K = 00)                         |

|-------|-------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------|

| 0     | 1     | $R_n + (AC \& K) + CI \rightarrow R_n, AC$                                           | $R_n + AC + CI \rightarrow R_n, AC$                                      | $R_n + CI \rightarrow R_n, AC$                     |

|       | 2     | $M + (AC \& K) + CI \rightarrow AT$                                                  | $M + AC + CI \rightarrow AT$                                             | $M + CI \rightarrow AT$                            |

|       | 3     | -                                                                                    | -                                                                        | сдвиг AT вправо                                    |

| 1     | 1     | $K \vee R_n \rightarrow PA;$<br>$R_n + K + CI \rightarrow R_n$                       | $11 \rightarrow PA$<br>$R_n - 1 + CI \rightarrow R_n$                    | $R_n \rightarrow PA$<br>$R_n + CI \rightarrow R_n$ |

|       | 2     | $K \vee M \rightarrow PA;$<br>$M + K + CI \rightarrow AT$                            | $11 \rightarrow PA$<br>$M - 1 + CI \rightarrow AT$                       | $M \rightarrow PA$<br>$M + CI \rightarrow AT$      |

|       | 3     | $(\bar{A}T \vee K) + (AT \vee K) + CI \rightarrow AT$                                | $AT - 1 + CI \rightarrow AT$                                             | $\bar{AT} + CI \rightarrow AT$                     |

| 2     | 1     | $(AC \& K) - 1 + CI \rightarrow R_n$                                                 | $AC - 1 + CI \rightarrow R_n$                                            | $CI - 1 \rightarrow R_n$                           |

|       | 2     | $(AC \& K) - 1 + CI \rightarrow AT$                                                  | $AC - 1 + CI \rightarrow AT$                                             | $CI - 1 \rightarrow AT$                            |

|       | 3     | $(B \& K) - 1 + CI \rightarrow AT$                                                   | $B - 1 + CI \rightarrow AT$                                              | $CI - 1 \rightarrow AT$                            |

| 3     | 1     | $R_n + (AC \& K) + CI \rightarrow R_n$                                               | $R_n - AC + CI \rightarrow R_n$                                          | $R_n + CI \rightarrow R_n$                         |

|       | 2     | $M + (AC \& K) + CI \rightarrow AT$                                                  | $M + AC + CI \rightarrow AT$                                             | $M + CI \rightarrow AT$                            |

|       | 3     | $AT + (B \& K) + CI \rightarrow AT$                                                  | $B + AT + CI \rightarrow AT$                                             | $AT + CI \rightarrow AT$                           |

| 4     | 1     | $R_n \& (AC \& K) \rightarrow R_n;$<br>$CI \vee (R_n \& AC \& K) \rightarrow C0$     | $R_n \& AC \rightarrow R_n;$<br>$CI \vee (R_n \& AC) \rightarrow C0$     | $0 \rightarrow R_n;$<br>$CI \rightarrow C0$        |

|       | 2     | $M \& (AC \& K) \rightarrow AT;$<br>$CI \vee (M \& AC \& K) \rightarrow C0$          | $M \& AC \rightarrow AT;$<br>$CI \vee (M \& AC) \rightarrow C0$          | $0 \rightarrow AT;$<br>$CI \rightarrow C0$         |

|       | 3     | $AT \& (B \& K) \rightarrow AT;$<br>$CI \vee (AT \& B \& K) \rightarrow C0$          | $AT \& B \rightarrow AT;$<br>$CI \vee (AT \& B) \rightarrow C0$          | $0 \rightarrow AT;$<br>$CI \rightarrow C0$         |

| 5     | 1     | $K \& R_n \rightarrow R_n;$<br>$CI \vee (R_n \& K) \rightarrow C0$                   | $R_n \rightarrow R_n;$<br>$CI \vee R_n \rightarrow C0$                   | $0 \rightarrow R_n;$<br>$CI \rightarrow C0$        |

|       | 2     | $K \& M \rightarrow AT;$<br>$CI \vee (M \& K) \rightarrow C0$                        | $M \rightarrow AT;$<br>$CI \vee M \rightarrow C0$                        | $0 \rightarrow AT;$<br>$CI \rightarrow C0$         |

|       | 3     | $K \& AT \rightarrow AT,$<br>$CI \vee (AT \& K) \rightarrow C0$                      | $AT \rightarrow AT;$<br>$CI \vee AT \rightarrow C0$                      | $0 \rightarrow AT;$<br>$CI \rightarrow C0$         |

| 6     | 1     | $R_n \vee (AC \& K) \rightarrow R_n;$<br>$CI \vee (AC \& K) \rightarrow C0$          | $R_n \vee AC \rightarrow R_n;$<br>$CI \vee AC \rightarrow C0$            | $R_n \rightarrow R_n;$<br>$CI \rightarrow C0$      |

|       | 2     | $M \vee (AC \& K) \rightarrow AT;$<br>$CI \vee (AC \& K) \rightarrow C0$             | $M \vee AC \rightarrow AT;$<br>$CI \vee AC \rightarrow C0$               | $M \rightarrow AT;$<br>$CI \rightarrow C0$         |

|       | 3     | $AT \vee (B \& K) \rightarrow AT;$<br>$CI \vee (B \& K) \rightarrow C0$              | $AT \vee B \rightarrow AC;$<br>$CI \vee B \rightarrow C0$                | $R_n \rightarrow R_n;$<br>$CI \rightarrow C0$      |

| 7     | 1     | $R_n \oplus (AC \& K) \rightarrow R_n;$<br>$CI \vee (R_n \& AC \& K) \rightarrow C0$ | $R_n \oplus AC \rightarrow R_n;$<br>$CI \vee (R_n \& AC) \rightarrow C0$ | $\bar{R}_n \rightarrow R_n$<br>$CI \rightarrow C0$ |

|       | 2     | $M \oplus (AC \& K) \rightarrow AT;$<br>$CI \vee (M \& AC \& K) \rightarrow C0$      | $M \oplus AC \rightarrow AT;$<br>$CI \vee (M \& AC) \rightarrow C0$      | $\bar{M} \rightarrow AT$<br>$CI \rightarrow C0$    |

|       | 3     | $AT \oplus (B \& K) \rightarrow AT;$<br>$CI \vee (AT \& B \& K) \rightarrow C0$      | $AT \oplus B \rightarrow AT;$<br>$CI \vee (AT \& B) \rightarrow C0$      | $\bar{AT} \rightarrow AT$<br>$CI \rightarrow C0$   |

В таблице 3.3 во всех операциях при  $R=1$  в качестве операндов используется один из задаваемых кодом R регистров РОНО – РОН9, T, AC. При  $R = 2$ ,  $R=3$  вместо AT подставляется T или AC, также задаваемые кодом R. При F=0 и R=3 выполняется сдвиг AT вправо: AT[0] → СПО, AT[1] → AT[0], СПИ → AT[1]. Необходимо также помнить, что в таблице 3.3 все операции указаны для прямых значений В, М, К, СI, СПI. Поскольку на этих входах ЦПЭ стоят инверторы, коды В, М, К и переменные СI, СПI необходимо подавать на вход ЦПЭ инвертированными.

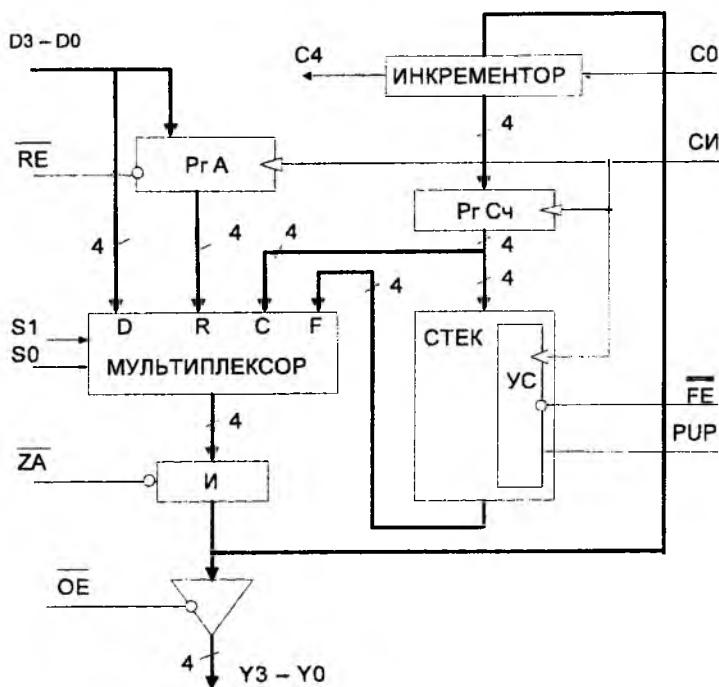

### **3.1.2. БИС БМУ для построения микропрограммных устройств управления**